#### Sistemas Digitais I

LESI - 2º ano

# Unit 7 - Sequential Systems Principles

#### João Miguel Fernandes www.di.uminho.pt/~jmf

ESCOLA DE ENGENHARIA

UNIVERSIDADE DO MINHO

DEP. DE INFORMÁTICA

# Sequential Circuits

- Combinational vs. Sequential Circuits

- inputs. Example: TV channel selector. A combinational circuit is one whose outputs depend only on its current

Logic circuits are classified as combinational or sequential.

- A sequential circuit is one whose outputs depend on its current inputs, with channel up/down buttons. but also on the past sequence of inputs. Example: TV channel selector

- means of a table that relates inputs with outputs. It is impossible to describe the behaviour of a sequential circuit by

- To know where to go next, we need to know where we are now

- The state of the system must be memorised

# Sequential Circuits

State (2) -

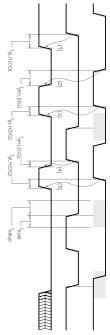

- The state changes occur at times specified by a clock signal

- A clock signal is <u>active high</u> if state changes occur at the clock's rising edge or when the clock is HIGH. Otherwise, it is <u>active low</u>.

- same direction. The clock period (T) is the time between successive transitions in the

- The clock frequency (f) is the reciprocal of the clock period (f=1/T).

- Two types of sequential circuits:

- <u>Feedback sequential circuits</u> use ordinary gates and feedback loops to obtain memory elements (latches and flip-flops).

- <u>Clocked synchronous state machines</u> use latches and flip-flops to create circuits that are regulated by a controlling clock signal.

# Sequential Circuits

- Summary .

- Combinational vs. Sequential Systems

- Bistable Elements

- Latches and Flip-flops

- State Machine Design

#### Sequential Circuits

- State (1) -

- The state of a sequential circuit is a collection of state variables whose for the circuit's future behaviour. values contain all the information about the past necessary to account

- In the TV channel example, the current channel number is the current

- Given the current state, we can always predict the next state as a function of the inputs.

- In a digital circuit, state variables are binary values

- A circuit with n binary state variables has 2n possible states

- Sequential circuits are also called finite-state machines

# Sequential Circuits

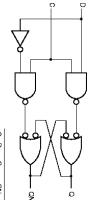

Bistable Elements (1) -

- of inverters forming a feedback loop. The simplest sequential circuit consists of a pair

- The circuit is called a <u>bistable</u>, since a digital analysis shows that it has two stable states.

0

- inverter to produce a HIGH output (as assumed initially) If Q is HIGH, the bottom inverter has a LOW output, which forces the top

- inverter to produce a LOW output (as assumed initially). If Q is LOW, the bottom inverter has a HIGH output, which forces the top

- We can use a single state variable (signal Q) to describe the state of the circuit. There are 2 possible states, Q=0 and Q=1.

Bistable Elements (2)

- The bistable element is so simple that it has no inputs, so its state cannot be

- stays there forever. When power is applied to the circuit, it randomly comes up in one state and

- perspective shows more aspects The analysis of the bistable from an analog

- and output voltages of both inverters are connections and the transfer functions constant values consistent with the loop The bistable is in equilibrium if the input

# Sequential Circuits

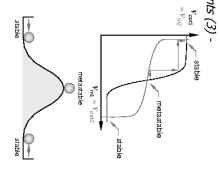

Bistable Elements (3) -

marked "stable"

The bistable is in equilibrium at the points

- have no valid logic values. The third equilibrium point, labelled "metastable", occurs when  $V_{out1}$  and  $V_{ou2}$

- If the circuit operates at the metastable point, it could stay there indefinitely.

- noise will tend to drive the circuit toward one of the stable points. The point is METAstable, because random

- Ball and hill analogy for metastable point.

#### Sequential Circuits

Latches and Flip-flops (1) -

- Latches and flips-flops are the basic building blocks of most sequential circuits.

- outputs only at times determined by a clocking signal. A flip-flop is a sequential device that samples its inputs and changes its

- A latch is a sequential device that watches all of its inputs continuously and changes its outputs at any time.

#### Sequential Circuits

Latches and Flip-flops (2)

- QN is usually the complement of Q.

- If S and R are both 0, the circuit behaves like the bistable element.

- Either S or R may be asserted to force the

- S sets or presets the Q output to 1. feedback loop to a desired state.

- R resets or clears the Q output to 0.

# Sequential Circuits

Latches and Flip-flops (3) -

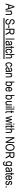

- inputs may be built with NAND gates An S-R latch with active-low set and reset

- previous one, with two major differences. The operation of this latch is similar to the

- First, S\_L and R\_L are active low, so the latch remembers its state, when S=R=1.

Second, when S\_L and R\_L are both asserted, both outputs go to 1 (not 0).

| 7       |

|---------|

| . Seq   |

| luent   |

| tial Ci |

| ircuits |

|         |

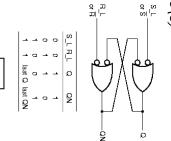

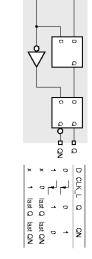

- An S-R latch is sensitive to its inputs at all times.

- It may be modified to be sensitive to these inputs only when an enabling input C is asserted.

- The circuit behaves like an S-R latch when C=1.

- It retains its state when C=0

| ×       | _ | _ | 0 | 0      | ဟ |

|---------|---|---|---|--------|---|

| ×       | _ | 0 | _ | 0      | D |

| 0       | _ | _ | _ | _      | 0 |

| last Q  | _ | _ | 0 | last Q | ۵ |

| last QN | _ | 0 | _ | ast QN | Q |

|         |   |   |   |        |   |

- Latches and Flip-flops (5) -

- Latches are needed to store bits of information.

- A D latch can be used for

- that purpose.

- The D latch can be built from an S-R latch.

- simultaneously. latches, where S and R may be asserted This latch eliminates the troublesome situation in S-R

- When C=1, the latch is open and the Q output follows the D input. When C=0, the latch is closed.

- × 0 last Q last QN 0 -

# Sequential Circuits

Latches and Flip-flops (6) -

- Delays exist for signals that propagate from the inputs to the Q output.

- There is a window of time (setup time and hold time) around the falling edge of C when the D input must not change.

- The latch's output is unpredictable, if those times are not respected

### Sequential Circuits

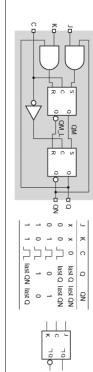

Latches and Flip-flops (7)

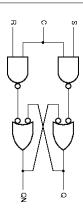

edge of the CLK signal. A <u>positive-edge-triggered D flip-flop</u> combines a pair of D latches to create a circuit that samples its D input and changes its outputs only at the rising

الم الم last Q last QN last Q last QN 0 0 -Š

0

- The first latch is called the master and it is open when CLK=0.

- When CLK goes to 1, the master latch is closed.

- begin of the interval, because the master is closed The second latch, the slave, is open while CLK=1, but changes only at the

#### Sequential Circuits

Latches and Flip-flops (8)

## Sequential Circuits

Latches and Flip-flops (9) -

- Some D flip-flops have asynchronous inputs that are used to force its state, independent of the CLK and D inputs.

- These inputs (PR and CLR) behave like the set and reset inputs on an S-R latch.

- They should be used for initialisation and testing purposes

- Some D flip-flops have the possibility to hold the last value stored. This is accomplished by adding an enable input.

|         |        |         |    | 0        |   |

|---------|--------|---------|----|----------|---|

| ×       | ×      | 0       | -  | _        | Z |

| -       | 0      | Ļ       | L- | <u>-</u> | 웃 |

| last Q  | last Q | last Q  | _  | 0        | Ð |

| last QN |        | last QN | 0  | -        | Ñ |

# Sequential Circuits

Latches and Flip-flops (10) -

- S-R latches are useful for control applications, where we may have independent conditions for setting/resetting a control bit. If the control bit is supposed to change only at certain times with respect to a clock signal, we need an S-R flip-flop.

IJ S

- Latches and Flip-flops (11) -

- The problem of what to do when S and R are both asserted is solved in a master/slave J-K flip-flop.

- The J and K inputs are analogous to S and R.

- However, asserting J asserts the master's S input only if Q=0.

- Asserting K asserts the master's R input only if Q=1.

- Thus, if J and K are asserted simultaneously, the flip-flop goes to the opposite of its current state.

# 7. Sequential Circuits

- Latches and Flip-flops (12) -

A <u>T flip-flop</u> changes state every tick of the clock

- The signal on the flip-flop's Q output has half the frequency of the T input.

- D and J-K flip-flops can be used to build a T flip-flop

# 7. Sequential Circuits

- Latches and Flip-flops (13) -

A T flip-flop can have an enable input

The flip-flop changes state at the triggering edge of the clock, only if the enable signal EN is asserted.

D and J-K flip-flops can be used to build a T flip-flop with enable.

#### Sequential Circuits

- State Machine Design (1) -

- A finite state machine (FSM) can be formally defined as the quintuple <s, I, O, F, G>, where:

- S represents the set of states.

- $^ \;$  I represents the set of inputs.

- o represents the set of outputs.

- F represents the next-state function

- G represents the output function.

- The F function assigns to every pair of state and input combination another state (F: SxI→S).

- The G function determines the output values in the present state

#### 7. Sequential Circuits

- State Machine Design (2) -

- There are 2 types of FSMs, which correspond to 2 different definitions of the output function G.

- For the Moore type, the G function is state-based (G:S→O).

- An output symbol is assigned to each state of the FSM.

- For the Mealy type, the G function is input-based (G:SxI→O).

- An output symbol is defined by a pair of state and input symbol.

- The FSM model assumes that time is divided into uniform intervals and that transitions occur only at the beginning of each time interval.

- There is a clock signal that defines the time intervals, called <u>clock cycles</u>

- Each FSM model can be implemented with flip-flops and logic gates.

# 7. Sequential Circuits

- State Machine Design (3) -

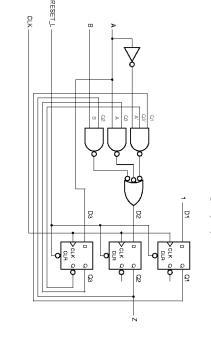

General structure of a clocked synchronous <u>Mealy State Machine</u>.

- The <u>State Memory</u> is a set of flip-flops that store the current state of the machine. The flip-flops are connected to a common clock signal.

- Both F and G are strictly combinational circuits

- State Machine Design (4) -

General structure of a clocked synchronous <u>Moore state machine</u>:

- The only difference between Mealy and Moore machines is in how the outputs are generated.

- To simplify the G block to just wires, we can use the <u>output-coded state</u> <u>assignment</u>, where the state variables serve as outputs.

# he stens to design a clocked synchronous state mach

- State Machine Design (5) -

Sequential Circuits

- The steps to design a clocked synchronous state machine are:

- Read the natural language description or specification of the system.

- Draw a state diagram, using mnemonic names for the states.

- Construct a state/output table.

- (Optional) Minimise the number of states in the table.

- Choose a set of state variables and assign state combinations to each state.

Substitute the state names for the corresponding state combinations in the ta

- Substitute the state names for the corresponding state combinations in the table.

Choose a flin-flor time for the state manner.

- Choose a flip-flop type for the state memory.

- Construct an excitation table that shows the excitation values required to obtain the desired next state for each state/input combination.

- Derive excitation equations.

- Derive output equations.

#### 7. Sequential Circuits

- State Machine Design (6) -

Example of a state machine problem:

- Design a state machine with inputs A and B, and output Z that is 1 if:

- A had the same value at each of the two previous clock ticks, or

- B has been 1 since the last time that the first condition was true.

- Otherwise, the Z output is 0.

- Right now, the meaning of the specification may not be clear

- The designer has to transform an ambiguous specifications written in natural language into an unambiguous <u>state table</u>.

- The machine is of Moore type, since the output depends only on the current state, that is, what happened in previous clock periods.

#### 7. Sequential Circuits

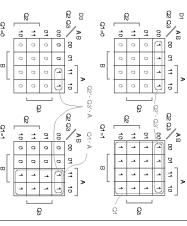

- State Machine Design (7)

|                           | n  | 3  | 2 A B |   | 5 | 7 | N.                        | n | 3 | 2 A B | _ " | -  |

|---------------------------|----|----|-------|---|---|---|---------------------------|---|---|-------|-----|----|

| Meaning                   | co | 00 | 01    | = | 2 | N | Meaning                   | s | 8 | 2     | l   | Ι_ |

| Initial state             | Z  |    |       |   |   | 0 | Initial state             | Ξ | æ | AO    | Α   |    |

|                           |    |    |       |   |   |   | Got a 0 on A              | B |   |       |     |    |

|                           |    |    |       |   |   |   | Cort of Core A            | Þ |   |       |     |    |

|                           |    |    |       |   |   |   | COLS LOU W                | A |   |       |     |    |

|                           |    |    |       |   |   |   |                           |   |   |       |     |    |

|                           |    |    |       |   |   |   |                           |   |   |       |     |    |

|                           |    |    | SON # | * |   |   |                           |   |   | s,    | *   |    |

|                           |    |    |       |   |   |   |                           |   |   |       |     |    |

|                           |    |    | ΑB    | В |   |   |                           |   |   | AB    | В   |    |

| Meaning                   | S  | 8  | 01    | = | 2 | И | Meaning                   | S | 8 | 2     | =   |    |

| Initial state             | Z  | ₹  | ₹     | 2 | Ā | 0 | Initial state             | Ī | ₹ | B     | 2   |    |

| Got a 0 on A              | ₿  | Š  | QK    | Α | A | 0 | Got a 0 on A              | ₿ | ě | ę     | ₹   |    |

| Got a 1 on A              | A  |    |       |   |   | 0 | Got a 1 on A              | P | 8 | B     | ç   |    |

| Got two equal A inputs OK | 9  |    |       |   |   | _ | Got two equal A inputs OK | ę |   |       |     |    |

|                           |    |    |       |   |   |   |                           |   |   |       |     |    |

|                           |    |    | š,    | * |   |   |                           |   |   | š,    | *   |    |

# 7. Sequential Circuits

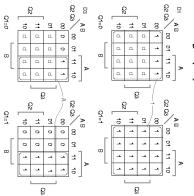

- State Machine Design (8) -

|                           |          |              | A D    | 00  |          |   |                     |        |              | ΑB  | Ø           |        |

|---------------------------|----------|--------------|--------|-----|----------|---|---------------------|--------|--------------|-----|-------------|--------|

| Meaning                   | s        | 8            | 2      | =   | ಠ        | Z | Meaning             | S      | 8            | 2   | =           | 5      |

| Initial state             | Z        | ₽            | ₹      | Ä   | Þ        | 0 | Initial state       | Ξ      | ₹            | ₹   | ž           | Ä      |

| Got a 0 on A              | ₿        | 읒            | Š      | Ä   | Þ        | 0 | Got a 0 on A        | ₿      | 8            | 086 | 2           | A      |

| Got a 1 on A              | Þ        | ₿            | ₿      | è   | ç        | 0 | Got a 1 on A        | A      | ₿            | ₿   | <u>Q</u>    | QK.    |

| Got two equal A inputs OK | Š        | ~            | Š      | Š   | ~        | _ | Two equal, A=0 last | 000    |              |     |             |        |

|                           |          |              |        |     |          |   | Two equal, A=1 last | OK1    |              |     |             |        |

|                           |          |              |        | š   |          |   |                     |        |              | s*  | *           |        |

|                           |          |              | АВ     | 8   |          |   |                     |        |              | ΑB  | B           |        |

| Meaning                   | s        | 8            | 01     | =   | 5        | Z | Meaning             | s      | 8            | 10  | =           | 5      |

| Initial state             | NIT      | ₽            | ₹      | Ā   | A        | ٥ | Initial state       | Π      | ₹            | ₹   | 2           | A      |

| Got a 0 on A              | ₿        | 0 <u>K</u> 6 | 0<br>6 | Ä   | <u>*</u> | 0 | Got a 0 on A        | ₽      | 0 <u>K</u> 6 | OK6 | <u>&gt;</u> | A      |

| Got a 1 on A              | <u>*</u> | ₿            | ₿      | Š.  | Q<br>S   | 0 | Got a 1 on A        | A      | ₿            | ₿   | <u>Q</u>    | Q<br>S |

| Two equal, A=0 last       | 0<br>80  | 000          | 0<br>6 | OK. | Þ        | _ | Two equal, A=0 last | 086    | 8            | 046 | Ŏ<br>Z      | Ä      |

| Two equal, A=1 last       | Q<br>Z   |              |        |     |          | _ | Two equal, A=1 last | Ŏ<br>Z | 8            | 040 | Ŏ<br>Z      | OK.    |

|                           |          |              | (0)    | š,  |          |   |                     |        |              | s,  | *           |        |

#### 7. Sequential Circuits

State Machine Design (9)

- The next step is to determine how many binary variables are needed to represent the states in the <u>state table</u>.

- After that, specific combinations are assigned to each state

- The binary combination of state variables assigned to a particular state is a coded state.

- With n flip-flops, 2<sup>n</sup> states can be coded.

- The number of flip-flops needed to code s states is 「log₂s ].

- In our problem, there are 5 states, so 3 flipflops are required.

|         | 용 | 0<br>KO  | Ą | ΑO | N | us |

|---------|---|----------|---|----|---|----|

|         | Ą | 0<br>6   | ð | 0K | Ą | 99 |

|         | 엉 | 용        | ₹ | 용  | ₹ | 01 |

| eo<br>* | 었 | 용        | 용 | ¥  | ¥ | ** |

|         | 용 | <u>*</u> | 욧 | A  | A | 10 |

|         | - | -        | 0 | 0  | 0 | N  |

State Machine Design (10) -

There are several alternatives to code the 5 states

|               |                   | Assig               | Assignment       |                         |

|---------------|-------------------|---------------------|------------------|-------------------------|

| State<br>Name | Simplest<br>Q1–Q3 | Decomposed<br>Q1–Q3 | One-hot<br>Q1-Q5 | Aimost One-hot<br>Q1–Q4 |

| N             | 000               | 000                 | 00001            | 0000                    |

| ₹             | 001               | 100                 | 00010            | 0001                    |

| Ħ             | 010               | 101                 | 00100            | 0010                    |

| 9             | 01.1              | 110                 | 01000            | 0100                    |

| OKI           | 100               | 111                 | 10000            | 1000                    |

- integers in binary counting order. The simplest assignment of s coded states is to use the first s binary

- output equations and resulting logic circuit. This assignment does not always lead to the simplest excitation equations,

# Sequential Circuits

State Machine Design (11) -

- The state assignment has a major impact on circuit cost

- It may interact with other factors, such as the choice of storage elements and the realisation approach for excitation and output logic.

- How to choose the best state assignment for a given problem?

- In general, the only formal way to find the "BEST" assignment is to try ALL the assignments.

- That is not possible to do by hand!!! For our example, there are 6.720 different ways to assign the 3-bit combinations to the 5 states

- Designers must rely on practical guidelines to achieve reasonable state assignments.

#### Sequential Circuits

State Machine Design (12)

- Guidelines for state assignment:

- Choose an initial coded state into which the machine can easily be forced at reset (typically, 000...0 or 111...1).

- Minimise the number of state variables that change on each transition.

- Maximise the number of state variables that don't change in a group of related states.

- assignment is established for the first, a similar assignment (differing in one bit) should be used for the second. Exploit symmetries in the problem specification and the corresponding symmetries in the state table. If one state or group means almost the same thing as another, once an

- Decompose the set of state variables into individual bits or fields, where each one has a well defined meaning with respect to the input effects or the output behaviour.

Consider using more than the minimum number of state variables to make possible a decomposed assignment.

#### Sequential Circuits

State Machine Design (13)

- Some of the previous guidelines were used in the decomposed state assignment

- INIT is 000, which is easy to force with the asynchronous CLR input of the flip-flops.

Name Name AO AO OKO

100

Decomposed Q1-Q3

- working. Q1 is used to indicate whether or not the actual state is INIT. INIT is never re-entered, once the machine is

- Q2,Q3 are used to distinguished among the other 4 states

- Q3 gives the previous value of A.

- state. Q2 indicates that the condition for a 1 output are satisfied in the current

# Sequential Circuits

- State Machine Design (14) -

- state machine. The one-hot state assignment can be adapted to any Name Name INIT A0 A1 OK0

- This assignment uses more than the minimum number of state variables: it uses 1 bit per state.

00001

0000

- This usually leads to small excitation equations,

- since each flip-flop must be set to 1 for transitions into only one state

- The almost one hot assignment uses the no-hot combination for the initial

- This eases the reset of the machine, since the initial state is 00...0.

# Sequential Circuits

State Machine Design (15) -

- number of state variable combinations. There are unused state codes when the number of states is less than the

- How to consider those unused states?

- In a minimal risk approach, it is assumed that the machine may go to an unused state, due to a hardware failure, for example.

- For all the unused states, an explicit transition to a safe state is made.

- an unused state. In a minimal cost approach, it is assumed that the machine will never enter

- The next state entries of the unused states can be marked as "don't cares'

State Machine Design (16) -

- corresponding code states. A transition table is obtained by substituting the state names by the

- current coded state and input. The transition table shows the next coded state for each combination of

- decomposed state assignment. transition table is obtained by using the For the state machine example, the

- needed to make the machine go to the desired next coded state. that shows the flip-flop excitation values The next step is to write an excitation table

|           | 111 | 110      | 101 | 100 | 000 | Q1 Q2 Q3 |    |  |

|-----------|-----|----------|-----|-----|-----|----------|----|--|

|           | 100 | 110      | 100 | 110 | 100 | 99       |    |  |

| 9         | 110 | 110      | 100 | 110 | 100 | 01       | `  |  |

| 01*02*03* | 111 | 111      | 111 | 101 | 101 | 11       | AB |  |

| *         | 111 | 101      | 111 | 101 | 101 | 10       |    |  |

|           | _   | <b>-</b> | 0   | 0   | 0   | 7        |    |  |

# Sequential Circuits

State Machine Design (17) -

- The structure and content of the excitation table depend on the type of flip-flop (D, J-K, T, etc.) being used.

- Nowadays, most state-machine designs use D flip-flops, because of their availability in both discrete packages and PLDs, and their ease of use.

- The characteristic equation of a D flip-flop is:

- labels. For D flip-flops, the excitation table is identical to the transition table, except for the

|          |     | 3   | ٩       |     |          |

|----------|-----|-----|---------|-----|----------|

| Q1 Q2 Q3 | 99  | 93  | 11      | 10  | 7        |

| 000      | 100 | 100 | 101     | 101 | 0        |

| 100      | 110 | 110 | 101     | 101 | 0        |

| 101      | 100 | 100 | 111     | 111 | 0        |

| 110      | 110 | 110 | 111     | 101 | <b>-</b> |

| 111      | 100 | 110 | 111     | 111 | -        |

|          |     | 9   | 9 22 29 |     |          |

#### Sequential Circuits

State Machine Design (18) -

- The excitation table is like a truth table for 3 combinational functions (D1,D2,D3) of 5 variables (A,B,Q1,Q2,Q3).

- maps, to find minimal expressions for each function. The information in the excitation table can be transferred to Karnaugh

- combinations, since the information for the unused states is not The excitation table does not specify functional values for all input

- minimal risk and minimal cost. For our example, we will take the two approaches previously referred:

### Sequential Circuits

State Machine Design (19) -

- is 000. In a minimal-risk approach, the next state for each unused state

- expressions can be obtained:

D1 = Q1+Q2'-Q3'

D2 = Q1-Q3'-A'+Q1-Q3-A+Q1-Q2-B

D3 = Q1-A+Q2'-Q3'-A From the maps the following

- Z is active for states 110 and 111 z = 01.02.03' + 01.02.03

# Sequential Circuits

- State Machine Design (20) -

- In a minimal-cost approach, the is a "don't-care" next state for each unused state

- expressions can be obtained: From the maps the following

- D3 = A D2 = Q1·Q3'·A'+Q3·A+Q2·B

- Z is active for states 110 and 111 and don't-care for the unused states.

Z=Q2

# 7. Sequential Circuits

- State Machine Design (21) -

- State Machine Design (22) -

- State diagrams are often used to design state machines.

- Designing a state diagram is similar, but simpler, to design a state table.

- A state diagram can contain some ambiguities, which is not possible in a state table.

- In an improperly constructed state diagram, the next state for some input combinations may be unspecified, which is undesirable.

- It is also possible that multiple next states exist for the same input combination.

# Sequential Circuits

- State Machine Design (23) -

- The next example is a state machine that control the tail lights of a car.

- The machine has 2 input signals, LEFT and RIGHT.

- It also has an emergency HAZ input that makes the 6 lights to flash

#### 7. Sequential Circuits

- State Machine Design (24) -

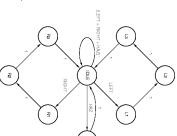

State diagram and Output table for the car lights controller.

| State | 5 | Б | ⋝ | ₹ | 88 | RC |

|-------|---|---|---|---|----|----|

| E E   | 0 | 0 | 0 | 0 | 0  | 0  |

| ュ     | 0 | 0 | - | 0 | 0  | 0  |

| 2     | 0 | - | - | 0 | 0  | 0  |

| ធ     | _ | _ | _ | 0 | 0  | 0  |

| 丑     | 0 | 0 | 0 | _ | 0  | 0  |

| 팑     | 0 | 0 | 0 | - | _  | 0  |

| Ð     | 0 | 0 | 0 | - | _  | _  |

| ĘŖ    | _ | _ | _ | _ | _  | _  |

Multiple inputs asserted simultaneously (LEFT and HAZ at IDLE) are not handled.

### 7. Sequential Circuits

State Machine Design (25) -

- Priority was given to the HAZ input.

- When LEFT and RIGHT are asserted simultaneously, it is assumed that an emergency is requested.

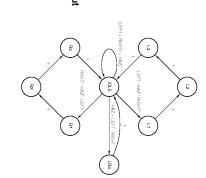

- The new state diagram is unambiguous

- The transition expressions on the arcs leaving the same state are mutually exclusive and all-inclusive.

- No two expressions are 1 for the same input combination.

- Some expression is 1 for every input combination

#### 7. Sequential Circuits

- State Machine Design (26) -

- Once a left- or right-turn cycle has begun, if must be finished even if an emergency is requested.

- It is safer to have the machine go into LR3 state as soon as possible.

- There are 8 states, so 3 flip-flops are needed to synthesise the circuit.

| ER3 | R3 |   |   |   |   |   |   |    |

|-----|----|---|---|---|---|---|---|----|

| -   | -  | - | - | 0 | 0 | 0 | 0 | Q2 |

|     | -  |   |   |   |   |   | 0 |    |

|     | 0  |   | _ | 0 | - | - | 0 | QB |

# 7. Sequential Circuits

- State Machine Design (27) -

| ß   | ß | ð        | a        | Transition Expression | å   | Q2 | ç | Ş |

|-----|---|----------|----------|-----------------------|-----|----|---|---|

| E   | 0 | 0        | 0        | (LEFT + RIGHT+ HAZ)   | Ē   | ۰  | ٥ | 0 |

| DLE | 0 | 0        | 0        | LEFT · HAZ' · RIGHT'  | Ξ   | 0  | 0 | - |

| E   | 0 | 0        | 0        | HAZ + LEFT - RIGHT    | ER3 | -  | 0 | 0 |

|     | 0 | 0        | 0        | RIGHT: HAZ': LEFT'    | 쪼   | -  | 0 | - |

| =   | 0 | 0        | -        | HAZ'                  | Б   | 0  | - | _ |

| Ξ   | 0 | 0        | -        | HAZ                   | E8  | -  | 0 | 0 |

| Б   | 0 | <b>-</b> | <b>-</b> | HAZ'                  | ខ   | 0  | - | 0 |

| Б   | 0 | -        | -        | HAZ.                  | 듄   |    | 0 | 0 |

| ឆ   | 0 | -        | 0        |                       | DLE | 0  | 0 | 0 |

| 포   | - | 0        | 1        | HAZ'                  | 20  | -  | - | _ |

| 포   | - | 0        | -        | HAZ                   | æ   |    | 0 | 0 |

| R   |   | -        | -        | HAZ'                  | 쭚   | -  | - | 0 |

| B   | 1 | -        | -        | HAZ                   | æ   | -  | 0 | 0 |

| B   | - | 1        | 0        | -                     | Ē   | 0  | 0 | 0 |

|     |   |          | ,        | -                     |     | 0  | 0 | 0 |

VHDL (1) -

- state machines. VHDL does not provide any special language constructs for specifying

- state machines were already introduced. Most of the VHDL features that are needed to support clocked synchronous

- A VHDL process and the simulator's mechanism for tracking signal changes form the basis for handling sequential circuits in VHDL.

- is true if the signal has changed value. The event attribute can be attached to a signal name to yield a value that

- describing state machines. This allows edge-trigger behaviour to be modelled.

The usage of enumerated types and CASE statements is also popular for

# Sequential Circuits

VHDL (2) -

with asynchronous clear.

Positive-edge-triggered D flip-flop

- behaviour on the CLK input The CLR input overrides any

- change on CLK. CLK' event is true for any

- edge-triggered behaviour. processes or statements with Two other ways to construct

- begin

process (CLK, CLR)

begin

if CLE='1' then Q <= '0'; QN <= '1';

elsif CLK event and CLK='1' then Q <= D; QN <=

end if;

end 'Poccess;

end 'Poccess;

end 'Poccess; entity VposDff is

port (CLK, CLR, D: in STD\_LOGIC;

Q, QN: cut STD\_LOGIC );

end VposDff; library IEEE; use IEEE.std\_logic\_1164.all; chitecture VposDff\_arch of VposDff is

Q <= D when CIK event and CIK='1' else Q reaction of the process of the proce

#### Sequential

Circuits - VHDL (4) -

|   | 양   | OK6    | A1     | ΑO  | Z  | cs |    |

|---|-----|--------|--------|-----|----|----|----|

|   | AO  | QK     | Ã      | OK0 | AO | 8  |    |

|   | 040 | 8      | B      | 8   | B  | 91 |    |

| ě | QK. | o<br>S | Q<br>S | ż   | ≥  | *  | AB |

|   | OK: | ¥      | 얁      | ¥   | ¥  | 10 |    |

|   | -   | μ      | 0      | 0   | 0  | N  |    |

```

library IEEE;

use IEEE.std_logic_1164.all;

architecture smexamp_arch of smexamp is

type Sreg_type is (INIT, AO, A1, OKO, OKI);

signal Sreg: Sreg_type;

begin

process (CLOCK) -- state-mac

begin

if CLOCK'event and CLOCK =

case Sreg is

when INIT -> if A-1

with Sreg select -- output values based on Z <-10' when INIT | AO | Al, '1' when OKO | OKI, '0' when others;

when others

end case;

end if;

end process;

when Al =>

when A0 =>

when OK1 =>

when OKO =>

elsif

elsif A

elsif.

lsif

f sif A-

then Srey < AD;

then Srey < AL; and if;

then Srey < AD; and if;

then Srey < OCL; and if;

then Srey < OCL; and if;

then Srey < OCL;

and B=0 then Srey < AL;

and B=0 then Srey < OCL;

then Srey < OCL;

then Srey < OCL;

then Srey < OCL;

and transitions

state

end if;

```

# Sequential Circuits

The first approach is to construct a state and output table by hand and the stated requirements. There are many possible ways of writing a VHDL program that meets the

- The first thing is to create an enumerated type (Sreg-type), whose manually convert it into a corresponding program.

- values are identifiers corresponding to the state names.

- machine's current state. It then declares a signal of that enumerated type, which is used to hold the

- The statement part of the architecture, has two concurrent statements

- The process is sensitive only to CLOCK and establishes all of the state

- The selected-assignment statement handles the machine's Moore output  ${\scriptstyle \mathrm{Z}.}$

# Sequential Circuits

- What about the state-assignment problem?

- it likes with the identifiers of an enumerated type. A synthesis tool is free to assign any integer values (or binary combinations)

- The typical assignment is the "simplest", using the order in which the states

- However, designers can force a different assignment.

- One way is to use VHDL's attribute statement.

- The VHDL language processor ignores this value, but passes this information to the synthesis tool

signal Sreg: architecture smexampe\_arch of smexamp is type Steq\_type is (INIT, AO, AL, OKO, OKI); type Steq\_type is attribute enum\_encoding of Sreg\_type: type is attribute enum encoding of Sreg\_type; type is signal Sreg: Sreg\_type; library IEEE;

use IEEE.std\_logic\_1164.all;

library SYNOPSYS;

use SYNOPSYS.attributes.all;

# Sequential Circuits

VHDL (6) -

Another way to force a state assignment is to define the state register more explicitly using standard logic data types.

```

architecture smexampc_arch of smexamp is

subtype Sreg_type is STD_LOGIC_VECTOR (1 to 4);

constant INIT: Sreg_type := "0000";

constant A0 : Sreg_type := "0001";

constant A1 : Sreg_type := "0100";

constant OKO : Sreg_type := "0100";

constant OKO : Sreg_type := "1000";

signal Sreg: Sreg_type;

library IEEE;

use IEEE.std_logic_1164.all;

```

.7

Car's light problem: state machine specified in VHDL.

```

architey Whird is

port (CLOTK, RESET, LERT, RIGHT, HAZ: in STD_LOGIC;

port (CLOTK, RESET, LERT, RIGHT, HAZ: in STD_LOGIC;

end;

architecture Whird_arch of Whird is

constant IDME STD_LOGIC_NETURE (1 to 6) := "000000";

constant IDME STD_LOGIC_NETURE (1 to 6) := "110000";

constant IDME STD_LOGIC_NETURE (1 to 6) := "1000000";

constant IDME STD_LOGIC_NETURE (1 to 6) := "0000011";

constant IDME STD_LOGIC_NETURE (1 to 6) := "000011";

constant IDME STD_LOGIC_NETURE (1 to 6) := "000011";

constant IDME STD_LOGIC_NETURE (1 to 6) := "010011";

constant IDME STD_LOGIC_NETURE (1 to 6) := "0100111";

constant IDME STD_LOGIC_NETURE (1 to 6) := "111111";

begin

when IDME Side IDME*'1' than IDMETS = IDME;

constant IDME Side IDME*'1' than IDMETS = IDME;

tif CLOTIC_NETURE (1 to 6) := "1111111";

than IDMETS = IDME;

constant IDME Side IDME*'1' than IDMETS = IDME;

than IDMETS = IDME;

when IDME side IDMETS = IDME;

when IDMETS = IDMETS

```