### Sistemas Digitais I

6

PLDs

Decoders

7-Segment Decoders

**Combinational Practices**

Summary

2º ano

Unit 6 - Combinational Design Practices

#### João Miguel Fernandes www.di.uminho.pt/~jmf

ESCOLA DE ENGENHARIA

UNIVERSIDADE DO MINHO

DEP. DE INFORMÁTICA

Multipliers

Adders, Subtractors and ALUs

Comparators

**XOR and Parity Circuits**

Multiplexers Encoders

#### <u>ნ</u> **Combinational Practices**

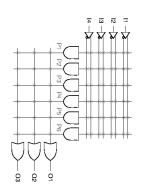

- The first PLDs were Programmable Logic Arrays (PLAs).

- programmed to realise any sum-of-products logic expression. A PLA is a combinational, 2-level AND-OR device that can be

- A PLA is limited by:

- the number of inputs (n)

- the number of outputs (m)

- the number of product terms (p)

- We refer to an "n x m PLA with p product terms". Usually, p <<  $2^n$ .

- An n x m PLA with p product terms contains p 2n-input AND gates and m p-input OR gates.

- PLDs (1) -

## **Combinational Practices**

PLDs (2)

- signal. a complemented version of the buffer that produces a true and Each input is connected to a

- indicated by Xs. Potential connections are

- establishing the needed connections. The device is programmed by

- The connections are made by

A 4x3 PLA with 6 product terms

## 6. Combinational Practices

PLDs (3) -

Compact representation of the 4x3 PLA with 6 product terms.

01 = 11·12 + 11·12·13·14' 02 = 11·13' + 11'·13·14 + 12 03 = 11·12 + 11·13' + 11'·12'·14'

### 6. Combinational Practices

- PLDs (4)

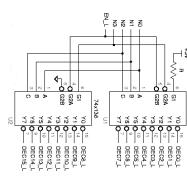

- Another PLD is PAL (Programmable Array

- the outputs. In a PAL, product terms are not shared by

A PAL device has a fixed OR array.

- Each output has a fixed and unique set of product terms that it can use

- A PAL is usually faster than a similar PLA

### 6. Combinational Practices

- PLDs (5) -

Part of the logic diagram of the PAL 16L8.

### 6. Combinational Practices

- Decoders (2) -

A 74x139 IC has two independent 2-to-4 decoders

| 13 14                                       | ω N O                                   |

|---------------------------------------------|-----------------------------------------|

| 26<br>28                                    | ឆ ≨ ធំ                                  |

| 270 0 12<br>271 0 11<br>272 0 10<br>273 0 9 | 3 3 3 3 7 7 8 8 8 8 8 8 8 8 8 8 8 8 8 8 |

|    | sındı |   |   | 0.4  | Outputs |

|----|-------|---|---|------|---------|

| ê. | œ     | ≯ | చ | ¥2_L | ᅼ       |

| -  | ×     | × | 1 | 1    | -       |

| 0  | 0     | 0 | _ | -    | -       |

| 0  | 0     |   |   |      | 0       |

| 0  |       | 0 | - | 0    | _       |

| 0  | -     | - | 0 | -    | -       |

### 6. Combinational Practices

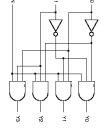

- Decoders (4) -

- Multiple decoders can be used to decode larger code words.

- The top decoder (U1) is enabled when N3 is 0, and the bottom decoder (U2) is enabled when N3 is 1.

- To handle larger code words, decoders can be cascaded hierarchically.

### 6. Combinational Practices

Decoders (1) -

- A <u>decoder</u> is a circuit that converts coded inputs into coded outputs.

- Usually, the input code has fewer bits than the output code.

- The most common decoder is an n-to-2<sup>n</sup> or binary decoder.

- A binary decoder is used when one of 2<sup>n</sup> outputs needs to be activated based on an n-bit input value.

| _ | spude | - |   | 0 | Sindin |   |

|---|-------|---|---|---|--------|---|

| 핃 | =     | ō | ¥ | ž | ≾      | శ |

| ٩ | ×     | × | 0 | ۰ | - 1    | 0 |

| - | 0     | 0 | 0 | 0 |        |   |

| - | 0     | - | 0 | 0 | -      | 0 |

| - | -     | 0 | 0 | - |        | 0 |

| - | -     | _ | _ | 0 | 0      | 0 |

### 6. Combinational Practices

Decoders (3) -

A 74x138 IC has one 3-to-8 decoder.

|   |   |   | ٩ | 1 | ٥        | - | o<br>N | ا<br>ا | 0 O                           | ō       |  |

|---|---|---|---|---|----------|---|--------|--------|-------------------------------|---------|--|

|   |   |   |   |   |          |   |        |        | ء ا                           |         |  |

| - | - | - | - | - | 1        | × | ×      | 0      | ਜੁ                            |         |  |

| 0 | 0 | 0 | 0 | 0 | 0        | × | -      | ×      | G2A_L                         |         |  |

| 0 | 0 | 0 | 0 | 0 | 0        | - | ×      | ×      | G2A_L G2B_L C                 | spadus  |  |

| - | - | 0 | 0 | 0 | 0        | × | ×      | ×      | c                             |         |  |

| 0 | 0 | - | - | 0 | 0        | × | ×      | ×      | œ                             |         |  |

| - | 0 | - | 0 | - | 0        | × | ×      | ×      | ≻                             |         |  |

|   |   | 1 |   |   |          | 1 |        | -      | 47_L                          |         |  |

| - | - | - | - | - | <b>-</b> | - | -      |        | ¥6_L                          |         |  |

| 0 |   | - | - |   | -        | - | -      |        | ¥5_L                          |         |  |

| - | 0 | - | - | - | <u>-</u> | - | -      | -      | ¥4<br> -                      | or4     |  |

| - | - | 0 | - |   | -        | - | -      |        | 47_L Y6_L Y5_L Y4_L Y3_L Y2_L | Outputs |  |

| - | - | - | 0 |   | <b>-</b> | - | -      |        | 12/2                          |         |  |

|   |   |   |   | 0 |          |   |        |        | בֻ                            |         |  |

### 6. Combinational Practices

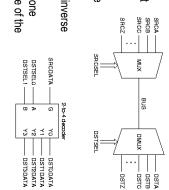

- Decoders (5) -

words, decoders can be cascaded hierarchically.

A 5-to-32 decoder can be built with one 2-to-4 and four 3-to-8 decoders.

To handle larger code

- The 2-to-4 decoder treats the high order bits.

- The 3-to-8 decoders treat the low-order bits.

#### 9 **Combinational Practices**

- There are several ways to write decoders in VHDL.

- The most primitive would be to write a structural description equivalent to the logic circuit on slide 7.

```

entity Visodes is

post (20.1) SH: an STD_LOGIC;

y0, Y1, Y2, Y3: out STD_LOGIC);

end Visodes y0 of Visodes is

supposent and yout (0.1 in STD_LOGIC);

end post time Visodes y0 of Visodes is

supposent and yout (0.1 in STD_LOGIC) o: out STD_LOGIC);

end post many post y0, 11, 12: an STD_LOGIC, O: out STD_LOGIC); end component

begin (0.1 inv yout map (0.1) NOT110;

UI: inv yout map (0.1) NOT110;

UI: and yout map (0.1) NOT110;

UI: and

ibrary IEEE;

se IEEE.std_logic_1164.all;

```

#### 9 Combinational Practices

Decoders (8)

Another alternative is using the behavioral style.

```

Y (= "00000000";

if (Gi and GZ and GZ) = '1' then

for i in 0 to 7 loop

if i=CONV_INTEGER(A) then Y(i) .

end if:

end if:

ss (G1, G2, G3, A)

iable i: INTEGER range 0 to 7;

```

### 6. Combinational Practices

7-Segment Decoders (2) -

|         | BIT D C B | 0 | - |   | 1 |   | -   | - | -  | - | - | - | - | -   | - | - | - | - |

|---------|-----------|---|---|---|---|---|-----|---|----|---|---|---|---|-----|---|---|---|---|

| _       | 0         | × | 0 | 0 | 0 | 0 | 0   | 0 | 0  | 0 | - | - | - | -   | - | - | - | - |

| spide,  | n         | × | 0 | 0 | 0 | 0 | 944 | - | ** | - | 0 | 0 | 0 | 0   | - |   |   | - |

|         | m         | × | 0 | 0 | - | - | 0   | 0 |    | - | 0 | 0 | - |     | 0 | 0 | - | - |

|         | >         | × |   | - | 0 | - | 0   | - | 0  | - | 0 | - | 0 | -   | 0 | - | 0 | - |

|         | ľ         |   |   |   |   |   |     |   |    |   |   |   |   |     |   |   |   |   |

|         |           | 0 | - | 0 | - | - | 0   | - | 0  | - | - | - | 0 | 0   | 0 | - | 0 | 0 |

|         | о<br>в    | 0 | - | - | - | - | -   | 0 | 0  | - | - | - | 0 | 0   | - | 0 | 0 | 0 |

| 0       | a         | 0 | - | - | 0 | - | -   | - | -  | - | - | - | 0 | 1   | 0 | 0 | 0 | 0 |

| Outputs | ۵         | 0 | - | 0 | - | - | 0   | - |    | 0 |   | 0 | - | -   | 0 | - | - | 0 |

| 'n      | •         | 0 | - | 0 | - | 0 | 0   | 0 |    | 0 | - | 0 | - | 0   | 0 | 0 | - | 0 |

|         | -         | 0 | - | 0 | 0 | 0 | -   | - | -  | 0 | - | - | 0 | 0 1 | - | - | - | 0 |

|         | 6         | 0 | 0 | 0 | - | - | -   | - | -  | 0 | - | - | - | -   | - | - | - | 0 |

|         |           |   |   |   |   |   |     |   |    |   |   |   |   |     |   |   |   |   |

- Exercise 1: decoder. of the 7-segment expressions for outputs Obtain minimised

- Exercise 2: segment decoder. description of a 7-Write a VHDL

### **Combinational Practices**

Decoders (7)

The second alternative is using the dataflow style

```

Feels a select Y_L-j or with h select Y_L-j or yellow he select Y_L-j or yellow he will have yellow he will have yellow he will have yellow. "Illillill" when yellow he will yellow yellow he will yellow yellow he will yellow yellow yellow yellow he will yellow yellow yellow he will yellow yell

entry V14AJ3 is

Fig. 16 and 17 and 1

chitecture V74x138_s of V74x138 is signal Y_L_i: STD_LOGIC_VECTOR (0 to 7);

```

### Combinational Practices

7-Segment Decoders (1)

- A 7-segment display is used in watches, calculators, and devices to show decimal data.

- A digit is displayed by illuminating a subset of the 7 line segments

as its output. A 7-segment decoder has a 4-bit BCD as its input and the 7-segment code

#### 6 **Combinational Practices**

Encoders (1)

- An encoder is a circuit whose output code has normally fewer bits than its input code.

- opposite function as a binary decoder. The simplest encoder to build is a 2<sup>n</sup>-to-n or binary encoder. It has the

- Equations for an 8-to-3 encoder: Y0 = |1 + |3 + |5 + |7 Y1 = |2 + |3 + |6 + |7 Y2 = |4 + |5 + |6 + |7

Only 1 input is active at a time. What happens if 2 inputs are asserted (ex: 12 and 14)?

#### <u>ნ</u> **Combinational Practices**

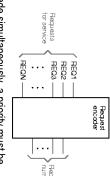

Encoders (2) -

- To implement a request encoder, the binary encoder does not work!

- It assumes that only 1 input

- If multiple requests can be made simultaneously, a priority must be assigned to the input lines.

- When multiple requests are made, the device (<u>priority encoder</u>) produces the number of the highest-priority requestor.

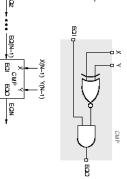

#### <u>.</u> **Combinational Practices** Encoders (3) Priority

- highest-priority asserted input, if any. Outputs A2-A0 contain the number of the Input I7 has the highest priority.

0 1 2 2 3 6 7

A A A

DLE

- The IDLE output is asserted if no inputs are

- Intermediate variable Hi is 1, if li  $H5 = 15 \cdot 16' \cdot 17'$   $H4 = 14 \cdot 15' \cdot 16' \cdot 17'$ is the highest priority 1-input: H6 = 16.17

- A0 = H1 + H3 + H5 + H7 A1 = H2 + H3 + H6 + H7 A2 = H4 + H5 + H6 + H7

- IDLE= 10'·11'·12'·13'·14'·15'·16'·17'

... (similar equations for H3-H0)

#### <u>ნ</u> **Combinational Practices**

<u>ნ</u>

**Combinational Practices**

- Multiplexers (1) -

- A multiplexer (mux) is a digital switch.

- It connects data from one of n sources to its output.

- sources, so  $s = | log_2 n |$ . The SEL input selects among the n

When EN=0, Y=0; When EN=1, the mux is working.

- Multiplexers are used in computers between the processor's registers and its ALU, to select among a set of registers which one is connected to

- ...∳o B SE b data output

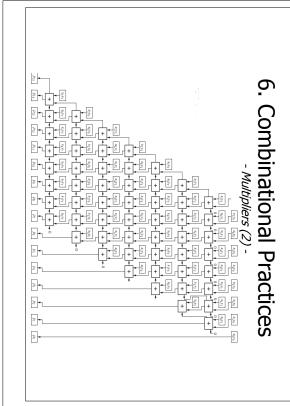

- A 74x151 IC has one 8-The select inputs are input, 1-bit multiplexer. Multiplexers (2) -

- active low. The enable input EN\_L is the MSB. named A,B,C, where C is

- Both active-low and high versions of the output are

- provided

|          | der | Ğ |          | Dut   | puts |

|----------|-----|---|----------|-------|------|

| EN_L C B | n   |   | с в А    | ۲ ۲ ۲ | Ļ    |

| _        | ×   | × | ×        | 0     | -    |

| 0        | 0   | 0 | 0        | 8     | é    |

| 0        | 0   | 0 | <b>-</b> | 9     | ď    |

| 0        | 0   | _ | 0        | 2     | D2   |

| 0        | 0   | - | -        | 2     | ă    |

| 0        | -   | 0 | 0        | 2     | ď    |

| 0        | -   | 0 | <b>-</b> | DS    | Βį   |

| 0        | -   | - | 0        | 8     | Ŕ    |

| ŀ        | -   | - | -        | 2     | ą    |

|          |     |   |          |       |      |

### 6. Combinational Practices

Multiplexers (3)

- multiplexer. A 74x157 IC has one 2-input, 4-bit

- The select input is S

16 18 28 28 38 38 38 48

- The enable input G\_L is active

- inputs appear at the outputs The truth table was extended and

- ø **#** ₹ ° 8 8 4 8 24 88 ¥ 4

### 6. Combinational Practices

Multiplexers (4) -

- on a bus. one of n sources of data to transmit A multiplexer can be used to select

- of m destinations. can be used to route the bus to one At the other end, a demultiplexer

- of a demultiplexer's. The function of a multiplexer is the inverse

- data input and s inputs to select one of the n=2s data outputs. A 1-bit, n-output demultiplexer has one

#### <u>.</u> **Combinational Practices**

Multiplexers (5) -

- It is easy to describe multiplexers in VHDL

- In the dataflow style, a SELECT statement is required

```

with Select Y =

with Select Y =

Abon "0.1",

Show "0.1",

Show "1.1",

Chors = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others; -- this creates an B-bit vector of

(others = "U") when others are also as a line of the line of t

architecture musainEb of musainEb is

begin

library IMEE;

use IMEE.std_logic_1104.all;

```

#### <u>.</u> Combinational Practices

XOR and Parity Circuits (1)

- whose output is 1, if exactly one of its inputs is An Exclusive-OR (XOR) gate is a 2-input gate

- An XOR gate produces a 1 output if its input are --00 \* 0 - 0

- inputs are the same. An Exclusive-NOR (XNOR) is just the opposite: it produces a 1 output if its

- The XOR operation is denoted by the symbol  $\oplus$

- $X \oplus Y = X' \cdot Y + X \cdot Y'$

### 6. Combinational Practices

XOR and Parity Circuits (3) -

- n XOR gates may be cascaded to form a circuit with n+1 inputs and a odd number of its inputs are 1. single output. This is a <u>odd-parity</u> circuit, because its output is 1 if an

- If the output of either circuit is number of its inputs are 1. circuit, whose output is 1 if an even inverted, we get an even-parity

#### <u></u> **Combinational Practices**

Multiplexers (6)

In a behavioural architecture, a CASE statement is used

case S is  $\begin{array}{lll} \text{cons} & \text{S is} \\ \text{show } & \text{for} & \text{sec } \lambda, \\ \text{show } & \text{for} & \text{sec } \lambda, \\ \text{show } & \text{for} & \text{sec } X \in \mathbb{R}, \\ \text{show } & \text{for} & \text{sec } X \in \mathbb{R}, \\ \text{show } & \text{constant} & \text{sec } X \in \mathbb{R}, \\ \text{show } & \text{constant} & \text{sec } X \in \mathbb{R}, \\ \text{show } & \text{constant} & \text{sec } X \in \mathbb{R}, \\ \text{show } & \text{constant} & \text{sec } X \in \mathbb{R}, \\ \text{show } & \text{constant} & \text{sec } X \in \mathbb{R}, \\ \text{show } & \text{constant} & \text{sec } X \in \mathbb{R}, \\ \text{show } & \text{show } & \text{sec } X \in \mathbb{R}, \\ \text{show } & \text{show } & \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } & \text{show } & \text{show } \\ \text{show } \\ \text{show } \\ \text{show } & \text{show } \\ \text{show } \\ \text{show } \\ \text{show }$ of mustings -- B-bit vector of 'U'

It is easy to customise the selection criteria in a VHDL multiplexer

### **Combinational Practices**

XOR and Parity Circuits (2)

There are 4 symbols for each XOR and XNOR function

- These alternatives are a consequence of the following rule:

- Any two signals (inputs or output) of an XOR or XNOR gate may be complemented without changing the resulting logic function.

- In bubble-to-bubble design we choose the symbol that is most expressive of the logic function being performed

# 6. Combinational Practices

XOR and Parity Circuits (4)

- VHDL provides the primitive operators xor and xnor.

- A 3-input XOR device can be specified in VHDL dataflow style program.

begin

Y = A xor B xor

end vxor3; entity vxor3 is

port (A, B, C: in SID\_LOGIC)

Y: out SID\_LOGIC);

end vxor3; architecture vxor3 of vxor3 is library HEEE; use HEEE.std\_logic\_1164.all;

### 9 **Combinational Practices**

XOR and Parity Circuits (5) -

behaviourally. can be specified A 9-input parity function

```

outity parity% is

port (I: in STD_LOGIC_NECTOR (1 to %);

EVEN, CDD: out STD_LOGIC.);

library IEEE;

use IEEE.std_logic_1104.all;

nd parity9;

rehitecture parity%p of parity% is

p := I(1);

p := I(1) = '1' then p := not p; end if;

if I(j) = '1' then p := not p; end if;

and Loop;

cop := p;

cop := not p;

smidble p : STD_LoGIC)

```

#### <u></u> **Combinational Practices**

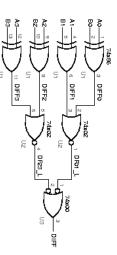

Comparators (1) -

- Comparing two binary words is a common operation in computers

- equal is a comparator. A circuit that compares 2 binary words and indicates whether they are

- and also indicate an arithmetic relationship (greater or less than) between Some comparators interpret their input as signed or unsigned numbers

- These circuits are often called magnitude comparators.

- XOR and XNOR gates can be viewed as 1-bit comparators

- the inputs are different. The DIFF output is asserted if

end process; end parity%p;

#### <u>ნ</u> Combinational Practices

Comparators (2)

The outputs of 4 XOR gates can be ORed to create a 4-bit comparator

- The DIFF output is asserted if any of the input-bit pairs are different.

- This circuit can be easily adapted to any number of bits per word

### Combinational Practices

Comparators (3) -

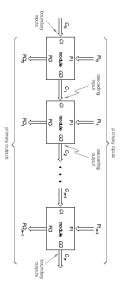

An iterative circuit is a combinational circuit with the following structure

- The circuit contains n identical modules, each of which has both primary inputs and outputs and cascading inputs and outputs.

- The left-most cascading inputs are usually connected to fixed values

### 6. Combinational Practices

Comparators (4) -

- so far: EQ; at each step to keep track of whether all of the bit-pairs have been equal Two n-bit values X and Y can be compared one bit at a time using a single bit

- Set EQ<sub>0</sub> to 1 and set *i* to 0.

If EQ<sub>i</sub> is 1 and X<sub>i</sub>=Y<sub>i</sub>, set EQ<sub>i+1</sub> to 1.

- 3. Increment *i*.4. If *i* < *n*, go to step 2. Else set EQ<sub>i+1</sub> to 0.

### 6. Combinational Practices Comparators (5) -

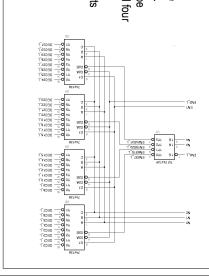

- Several MSI comparators have been developed commercially

- The 74x85 is a 4-bit comparator.

- and an equal output. It provides a greater-than output, a less-than output

- multiple chips to create comparators for more than 4 The 74x85 also has cascading inputs for combining

- AGTBOUT =  $(A>B) + (A=B) \cdot AGTBIN$ AEQBOUT =  $(A=B) \cdot AEQBIN$ ALTBOUT =  $(A<B) + (A=B) \cdot ALTBIN$

### 6. Combinational Practices

Comparators (6)

With three 74x85 circuits, a 12-bit comparator can be built.

### 6. Combinational Practices

- Comparators (7) -

- VHDL has comparison operators for all of its built-in types.

- Equality (=) and inequality (/=) operators apply to all types

- For array and record types, the operands must have equal size and structure, and the operands are compared component by component.

- VHDL's other comparison operators (>, <, >=, <=) apply only to integers, enumerated types and one-dimensional arrays of enumeration or integer types.

### 6. Combinational Practices

- Adders, Subtractors and ALUs (1)

- Addition is the most commonly performed arithmetic operation in digital systems.

- An <u>adder</u> combines two arithmetic operands using the addition rules.

- The same addition rules, and hence the same adders, are used for both unsigned and 2's complement numbers.

- An adder can perform subtraction as the addition of the minuend and the complemented subtrahend.

- A <u>subtractor</u> can also be built to perform subtraction directly.

- An <u>ALU</u> (Arithmetic and Logic Unit) performs addition, subtraction, and other logical operations.

### 6. Combinational Practices

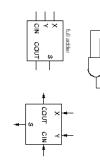

Adders, Subtractors and ALUs (2) -

- The simplest adder, called a <u>half adder</u>, adds two 1-bit operands X and Y, producing a 2-bit sum.

- The sum can range from 0 to 2, which requires two bits to express.

- The low-order bit of the sum may be named HS (<u>half sum</u>).

- The high-order bit of the sum may be named CO (carry out)

- The following equations can be written:

$HS = X \oplus Y = X \cdot Y' + X' \cdot Y$   $CO = X \cdot Y$

To add operands with more than one bit, carries between bit positions must be provided.

### 6. Combinational Practices

- Adders, Subtractors and ALUs (3)

- The building block for this operation is called a full adder.

- Besides the addend-bit inputs X and Y, a full adder has a <u>carry-bit input</u>, CIN.

- The sum of the 3 bits can range from 0 to 3, which can still be expressed with just two output bits, S and COUT.

- The following equations can be written:

S = X ⊕ Y ⊕ CIN

COUT = X:Y + X:CIN + Y:CIN

### 6. Combinational Practices

Adders, Subtractors and ALUs (4) -

- Two binary words, each with n bits, can be added using a ripple adder.

- A ripple adder is a cascade of n full-adders stages, each of which handles one bit.

- The carry input to the least significant bit (c<sub>0</sub>) is usually set to 0.

- The carry output of each full adder is connected to the carry input of the next most significant full adder.

#### 9 **Combinational Practices**

6

**Combinational Practices**

Adders, Subtractors and ALUs (6) -

Adders, Subtractors and ALUs (5) -

- The binary subtraction operation is analogous to binary addition

- A full subtractor has inputs X (minuend), Y (subtrahend) and BIN (borrow in) and outputs D (difference) and BOUT (borrow out)

- The following equations can be written:  $D = X \oplus Y \oplus BIN$

BOUT = X'·Y + X'·BIN + Y·BIN

These equations are similar to the equations for a full adder.  $= X \oplus Y' \oplus BIN'$

BOUT = X·Y' + X·BIN' + Y·BIN'

A full subtractor can be built from a full adder. X-Y = X+Y'+1

#### 9 Combinational Practices

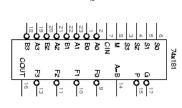

Adders, Subtractors and ALUs (7)

An  $\underline{\mathsf{ALU}}$  is a combinational circuit that can perform bit operands. several arithmetic and logical operations on a pair of b-

The operation to be performed is specified by a set of

- function-select inputs. functions to be performed. function-select inputs, allowing up to 32 different Typical MSI ALUs have 4-bit operands and three to five

- A 74x181 IC has one 4-bit ALU

- the M and S3-S0 inputs. The operation performed by the 74x181 is selected by

### <u>6</u> Combinational Practices

Adders, Subtractors and ALUs (8) -

|   | da.      | արսե     |    | Function                         |                   |

|---|----------|----------|----|----------------------------------|-------------------|

| 8 | 92       | ō.       | 98 | M=0 (arithmetic)                 | M = 1 (legic)     |

| ٵ | ۰        | ۰        | ۰  | F = A minus 1 plus CIN           | F=A               |

| 0 | 0        | 0        | -  | F = A · B minus 1 plus CIN       | F = A' + B'       |

| ۰ | 0        | -        | •  | F = A · B' minus 1 plus CIN      | F = A' + B        |

| 0 | 0        | <b>-</b> | 1  | F= 1111 plus CIN                 | F=1111            |

| 0 | -        | 0        | •  | F = A plus(A + B') plus CIN      | $F = A' \cdot B'$ |

| 0 | <b>-</b> | 0        | -  | F = A · B plus (A + B') plus CIN | F = 8(            |

| ۰ | -        | -        | 0  | F=A minus B minus 1 plus CIN     | F=A⊕B′            |

| ۰ | -        | -        | -  | F = A + B' plus CIN              | F = A + B'        |

| _ | 0        | 0        | 0  | F = A plus (A + B) plus CIN      | $F = A' \cdot B$  |

| - | 0        | 0        | -  | F = A plus B plus CIN            | F=A⊕B             |

| _ | •        | -        | 0  | F = A · B' plus (A + B) plus CIN | F = B             |

| _ | 0        | -        | -  | F = A + B plus CIN               | F=A+B             |

| _ | -        | 0        | 0  | F = A plus A plus CIN            | F=0000            |

| _ | _        | 0        | _  | F = A · B plus A plus CIN        | $F = A \cdot B'$  |

| - | -        | -        | 0  | F = A · B' plus A plus CIN       | $F = A \cdot B$   |

| - | -        | <u>.</u> | -  | F = A plus CIN                   | FHA               |

#### <u>ნ</u> Combinational Practices

Adders, Subtractors and ALUs (9) -

```

architecture vaddshr_arch of vaddshr is

begin

S <= A + B when SEL = '1' else C + D;

end vaddshr_arch;

entity vaddshr is

port (

library IBBB;

use IBBB.std_logic_l164.all;

use IBBB.std_logic_arith.all;

);

end vaddshr;

A, B, C, D: in SIGNED (7 downto 0);

SEL: in STD_LOGIC;

S: out SIGNED (7 downto 0)

```

### <u>ნ</u> **Combinational Practices**

- Multipliers (1) -

- The traditional algorithm to multiply binary numbers uses shifts and adds to obtain the result.

- However, it is not the only solution to implement a multiplier

- Given 2 n-bit inputs (X, Y), we can write a truth table that expresses the 2n-bit product  $P=X\times Y$  as a combinational function of X and Y.

- Most approaches to combinational multipliers are based on the traditional shift-and-add algorithm.

#### <u>.</u> Combinational Practices - Multipliers (3) -

```

library IEBE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

```

architecture vmul8x8i\_arch of vmul8x8i is begin p = X \* Y; end vmul8x8i\_arch;