# Sistemas Digitais I

LESI - 2º ano

Unit 5 - VHDL

# João Miguel Fernandes www.di.uminho.pt/~jmf

DEP. DE INFORMÁTICA ESCOLA DE ENGENHARIA UNIVERSIDADE DO MINHO

### 5. VHDL

Introduction -

- VHDL was developed, in the mid-1980s, by DoD and IEEE.

- VHDL stands for VHSIC Hardware Description Language; VHSIC stands for Very High Speed Integrated Circuit.

- VHDL has the following features:

- Designs may be decomposed hierarchically.

- Each design element has both an interface and a behavioural specification.

- Behavioural specifications can use either an algorithm or a structure to define the element's operation.

- Concurrency, timing, and clocking can all be modelled.

- The logical operation and timing behaviour of a design can be simulated.

### 5. VHDL

Entities and Architectures (1) -

- VHDL was designed with the principles of structured programming

- Pascal and Ada influenced the design of VHDL.

- internal details. An interface defines the boundaries of a hardware module, while hiding its

- module's inputs and outputs. A VHDL entity is a declaration of a

- A VHDL architecture is a detailed structure or behaviour. description of the module's internal

### 5. VHDL

- Summary -

- Design flow

- Entities and Architectures

- Types

- **Functions and Procedures**

- Libraries and Packages

- Structural Design

- Dataflow Design

- Behavioural Design

- Simulation Time Dimension

### 5. VHDL

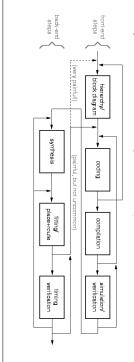

Design flow -

- VHDL started out as a documentation and modelling language, allowing the behaviour of designs to be specified and simulated.

- Synthesis tools are also commercially available. A synthesis tool can create logic-circuit structures directly from VHDL specifications.

### 5. VHDL

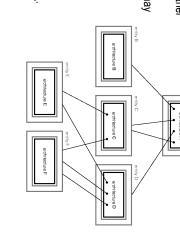

Entities and Architectures (2) -

- An architecture may use other

- A high-level architecture may multiple times. use a lower-level entity

- same lower-level entity. Multiple top-level architectures may use the

- hierarchical system design This forms the basis for

Entities and Architectures (3) -

In the text file of a VHDL program, the <u>entity declaration</u> and the <u>architecture definition</u> are separated.

entity Inhibit is

port (X,Y: in BIT;

Z: out BIT);

end Inhibit; architecture Inhibit\_arch of Inhibit is begin Z <= '1' when X='1' and Y='0' else '0'; end Inhibit\_arch;

- The language is not case sensitive.

- Comments begin with 2 hyphens (--) and finish at the end of the line

- VHDL defines many reserved words (port, is, in, out, begin, end, entity, architecture, if, case, ...).

### 5. VHDL

Entities and Architectures (5) -

Syntax of an architecture definition:

ax chitecture architecture.

The declarations

Signal declarations

Signal declarations

function definitions

function definitions

procedure definitions

procedure definitions

be 9.1.

concurrent statement concurrent-statement end architecture-name

- The declarations can appear in any order.

- In signal declarations, internal signals to the architecture are defined: signal signal-names: signal-type;

### 5. VHDL

- Туреs (2) -

Built-in operators for integer and boolean types.

|                |                 |                  |                 |          |                |             |          | ı                 |

|----------------|-----------------|------------------|-----------------|----------|----------------|-------------|----------|-------------------|

| *              | N<br>Q          | rem              | mod             | _        | *              | 1           | +        | Į,                |

| exponentiation | absolute value  | modulo remainder | modulo division | division | multiplication | subtraction | addition | integer Operators |

|                | not             | топх             | XOL             | TOF      | nand NAND      | 20          | and      | 500               |

|                | compl           | Exclu            | Exclu           | S<br>S   | NAND           | 욹           | AND      | Lean              |

|                | complementation | Exclusive NOR    | Exclusive OR    |          | -              |             |          | boolean Operators |

### 5. VHDL

Entities and Architectures (4) -

Syntax of an entity declaration:

signal-names : mode signal-type);

end entity-name; entity enity-name is

port(signal-names : mode signal-type,

signal-names : mode signal-type

- mode specifies the signal direction:

- in: input to the entity

- out: output of the entity

- buffer: output of the entity (value can be read inside the architecture)

- inout: input and output of the entity.

- signal-type is a built-in or user-defined signal type

### 5. VHDL

- Types (1) -

- All signals, variables, and constants must have an associated type.

- A  $\underline{\text{type}}$  specifies the set of valid values for the object and also the operators that can be applied it  $\Rightarrow$  ADT (similar concept to OO class).

- VHDL is a strongly typed language.

- VHDL has the following pre-defined types:

| it        | character | severity_level |

|-----------|-----------|----------------|

| it_vector | integer   | string         |

| oolean    | real      | time           |

|           |           |                |

- integer includes the range -2 147 483 647 through +2 147 483 647.

- boolean has two values, true and false.

- character includes the characters in the ISO 8-bit character set

### 5. VHDL

- Туреs (3) -

- User-defined types are common in VHDL programs.

- Enumerated types are defined by listing the allowed values

type type-name is (value-list); subtype subtype name is type name start to end;

subtype subtype name is type name start downto end;

constant constant name: type name := value;

| 1                             | ;(•-•      | H    | L',  | N.      | z',       | 11',    | ,0,     | 'X',    | ď             | type SID      |

|-------------------------------|------------|------|------|---------|-----------|---------|---------|---------|---------------|---------------|

| S                             | ł          | ł    | 1    | ł       | ł         | ł       | 1       | ł       | ł             | 덛             |

| LOGIC                         | Don't care | Neak | Neak | Neak    | High Impe | Forcing | Porcing | Forcing | Uninitialized | SID_ULOGIC is |

| STD LOGIC is resolved STD ULO | 0          | Ľ    | 0    | Unknown | Impedance | Ľ       | 0       | Unknown | Lized         | ^             |

| STO                           |            |      |      |         |           |         |         |         |               |               |

| 5                             |            |      |      |         |           |         |         |         |               |               |

- type traffic\_light is (reset, stop, start, go);

subtype bitnum is integer range 31 downto 0;

- constant BUS\_SIZE: integer := 32;

Туреs (4) -

Array types are also user-defined.

type type-name is array(range-type range start to end) of element-type; type type-name is array(range-type) of element-type; type type-name is array(range-type range start downto end) of element-type; type type-name is array(start downto end) of element-type; type type-name is array(start to end) of element-type;

constant MDRD\_LEN: integer := 32;

type word is array (MORD\_LEN-1 downto 0) of STD\_LOGIC;

tonstant NUM\_REGES: integer := 8;

type reg\_file is array (1 to NUM\_REGE) of word;

type statecount is array (traffic\_light\_state) of integer; type monthly\_count is array (1 to 12) of integer; type byte is array (7 downto 0) of STD\_LOGIC;

### 5. VHDL

Functions and Procedures (1) -

- A function accepts a set of arguments and returns a result

- The arguments and the result must have a type.

- Syntax of a function definition.

```

signal-hames : signal-type

seturn return-type is

type declarations

constant declarations

variable declarations

function definitions

function definitions

equential-statement

ction function-name(

signal-names : signal-type;

signal-names : signal-type;

```

begin

Z <= ButNot(X,Y);

end Inhibit\_archf;</pre> function ButNot (A, B: bit) return bit is

begin

if B = '0' then return A;

else return '0';

end ::architecture Inhibit\_archf of Inhibit is

### 5. VHDL

Functions and Procedures (3) -

- A procedure is similar to a function, but it does not return a result.

- Whereas a function call can be used in the place of an expression, a procedure call can be used in the place of a statement.

- Procedures allow their arguments to be specified with mode out or inout, so it is possible for a procedure to "return" a result.

### 5. VHDL

Туреs (5) -

Array literals can be specified by listing the values in parentheses: xyz := ('1','1','0','1','1','0','0','1'); abc := (0=>'0', 3=>'0', 9=>'0', others=>'1');

Strings can be used for STD\_LOGIC arrays:

xyz := "11011001";

abc := "011011111101111111";

Array slices can be specified: xyz(2 to 4)

abc(9 downto 0)

operator (&):

'0'&'1'&"12" is equivalent to "0112". Arrays and array elements can be combined with the concatenation

B (6 downto 0) &B (7) represents a 1-bit left rotate of the B array

### 5. VHDL

Functions and Procedures (2) -

convert a signal from one It is often necessary to type to another.

Assume that the following defined: unconstrained array type is

type

STD\_LOGIC\_VECTOR is

array (natural range

<>) of STD\_LOGIC;

begin

RESULT:= 0;

RESULT:= RESULT \* 2;

for Lin X'range loop

for Lin X'range loop

for Lin X'range loop

for Lin X'range loop

case X(L) is

when '0' | 'L' = NILL;

when '1' | 'R' = NESULT := RESULT + 1;

when others => null;

end loop;

return RESULT;

end Loop;

return RESULT;

end COMV\_INTEGER; function CONV\_INTEGER (X: STD\_LOGIC\_VECTOR) return INTEGER variable RESULT: INTEGER;

temp := ARG;

for i in 0 to SIZE-1 loop

for i in 0 to SIZE-2 loop

if (temp mod 2) = 1 then result(i) := '1';

else result(i) := '0';

end if;

end if;

temp := temp / 2;

end loop;

eturn result; function CONV\_STD\_LOGIC\_VECTOR (ARG: INTEGER; SIZE: INT

return STD\_LOGIC\_VECTOR is

variable result: STD\_LOGIC\_VECTOR (SIZE-1 downto 0);

variable temp: integer; ER; SIZE: INTEGER)

### 5. VHDL

Libraries and Packages (1) -

- A library is a place where the VHDL compiler stores information about a particular design project.

- For any design, the compiler creates and uses the work library

- A design may have multiple files, each containing different units

- When a file is compiled, the results are placed in the  $\mathtt{work}$  library

- Not all information needed in a design must be in the work library. A different projects. designer may rely on common definitions or functions across a family of

- A project can refer libraries containing shared definitions

library ieee;

Libraries and Packages (2) -

- A <u>package</u> is a file with definitions of objects (signals, types, constants, functions, procedures, component give access to types and the like. analysed entities and architectures, but does not Specifying a library gives access to any previously

- A design can use a package: declarations) to be used by other programs.

use ieee.std\_logic\_1164.all;

Within the ieee library, the definitions are on file std\_logic\_1164.

### 5. VHDL

Structural Design (1) -

- The body of an architecture is a series of concurrent statements.

- concurrent statements in the same architecture body. Each concurrent statement executes simultaneously with the other

- hardware. Concurrent statements are necessary to simulate the behaviour of

- The most basic concurrent statement is the component statement.

```

label: component-name port map (port=>signall, port2=>signal2,

label: component-name port map (signall, signal2, ..., signaln);

```

- component name is the name of a previously defined entity.

- One instance of the entity is created for each component statement.

### **YHDL**

Structural Design (2) -

- Before being instantiated, a component must be declared in the component declaration in the architecture's definition.

- A component declaration is essentially the same as the port declaration part of an entity declaration.

```

signal-names: mode signal-type);

end component;

component component-name

port(signal-names : mode signal-name);

signal-names : mode signal-name;

```

The components used in an architecture may be those previously defined as part of a design, or they may be part of a library.

### YHDL

Structural Design (3) -

```

begin

UI: INV port map (N(2), N2_L);

U2: INV port map (N(1), N2_L);

U3: INV port map (N(1), N1_L);

U3: INV port map (N(1), N1_L);

U4: AND2 port map (N3_L, N(1), N3L_N0);

U5: AND2 port map (N3_L, N(1), N(1), N(1), N(1), N(1);

U6: AND3 port map (N(1), N(1), N(1), N(1), N(1);

U6: AND3 port map (N(1), N(1), N(1), N(2_N1_N0);

U7: AND3 port map (N(1), N(1), N(1), N(2_N1_N0);

U7: AND3 port map (N(1), N(1), N(1), N(1), N(1), N(1), N(1), N(1), N(1);

U6: AND3 port map (N(1), N(1), N(1),

Library IEEE;

use IEEE.std_logic_1164.all;

entity prime is

port ( N: in STD_LOGIC_VECTOR (3 downto 0); F: out STD_LOGIC );

end prime;

architecture primel_erch of prime is signal NJ_L, N2_L, N1_L; STD_LOGIC; signal NJ_L, N2_L, N1_L; STD_LOGIC; signal NJL,N0, NJL,N1_L,N1, N2_L,N1_N0, N2_N1L_N0; STD_LOGIC; end component; component INV poirt (IV, in STD_LOGIC; O: out STD_LOGIC); end component; component AND2 poirt (IV,II); in STD_LOGIC; O: out STD_LOGIC); end component; component AND3 poirt(IV,II,IV; in STD_LOGIC; O: out STD_LOGIC); end component; component AND3 poirt (IV,II,IV; in STD_LOGIC; O: out STD_LOGIC); end component; component OR4 poirt (IV,II,IV,IV; in STD_LOGIC; O: out STD_LOGIC); end component; component OR4 poirt (IV,II,IV,IV; in STD_LOGIC; O: out STD_LOGIC); end component; component OR4 poirt (IV,II,IV,IV; IV,IV; I

```

### 5. VHDL

Structural Design (4) -

- describes the structure of signals and entities that realise the entity. An architecture that uses components is a structural description, since it

- The generate statement allows repetitive structures to be created

```

label: for identifier in range generate concurrent-statement end generate;

```

```

begin

g1: for b in 1 to 8 generate

g1: INV port map (X(b), Y(b));

end generate;

end inv8_arch;

library IEEE;

use IEEE std_logic_1164.all;

use IEEE std_logic_1164.all;

entity inv6 is

port ( X: in SID_LOGIC_VECTOR (1 to 8);

you to stro_LOGIC_VECTOR (1 to 8);

end inv8;

component INV port (I; in STD_LOGIC; O: out STD_LOGIC); end component;

```

### 5. VHDL

- Structural Design (5) -

Generic constants can be defined in an entity declaration.

```

signal-names : mode signal-type);

end entity-name;

entity entity-name is

generic(constant-names: constant-type;

constant-names: constant-type;

constant-names: constant-type);

port(signal-names: mode signal-type;

signal-names: mode signal-type;

```

- is deferred until the entity is instantiated in another architecture, using a Each constant can be used within the respective architecture and the value component statement.

- Within the component statement, values are assigned to the generic constants using a generic map clause.

#### <u>.</u> **VHDL**

Structural Design (6) -

```

acchitecture businv_arch of businv is component INV port (I: in STD_LOGIC); end component; begin businv_arch of businv 0 generate gl: for b in NTD-1 downto 0 generate ul: INV port map (X(b), Y(b)); end generate; end generate; end businv_arch; end businv_arch;

entity businv is

generic (MIDTH: positive);

port ( X: art STD_LOGIC_VECTOR (MIDTH-1 downto 0);

Y: art STD_LOGIC_VECTOR (MIDTH-1 downto 0) );

library IEEE;

use IEEE.std_logic_1164.all;

```

#### <u>.</u> **VHDL**

Dataflow Design (1) -

- Other concurrent statements allow circuits to be described in terms of the flow of data and operations on it within the circuit.

- This gives origin to the dataflow description style.

- Syntax of concurrent signal assignments statements.

```

signal-name <= expression when boolean-expression else expression when boolean-expression else

<= expression;

expression when boolean-expression else expression;

```

### 5. VHDL

Dataflow Design (3) -

- Another concurrent statement is the selected signal assignment, which is similar to a typical CASE constructor.

- Syntax of selected signal assignments.

with expression select

signal-name <= signal-value when choices,

signal-value when choices,

signal-value when choices;

```

architecture prime4_arch of prime is begin with N select F = 11 when "0001", '1' when "0010", '2' when "0011" | "0101" | "0111", '1' when "0011" | "1101", '0' when others; end prime4_arch;

```

```

architecture prime5_arch of prime is begin with CONY_INTEGER(N) select P <= '1' when 1/2 | 5 | 7 | 11 | 13, end prime5_arch; end prime5_arch;

```

### 5. VHDL

Structural Design (7) -

```

architecture businv_ex_arch of businv_example is component businv generic (MIDHH: positive); generic (MIDHH: positive); port (X: in STD_LOGIC_VECTOR (MIDHH-1 downto 0)); you component; begin the property of the positive generic map (MIDHH-98) port map (IN8, OUT8); U: businv generic map (MIDHH-916) port map (IN8, OUT8); U: businv generic map (MIDHH-932) port map (IN8, OUT32); end businv_ex_arch;

entity businv_example is

port [IMS: in STD_LOGIC_VECTOR (7 downto 0);

OUTS: out STD_LOGIC_VECTOR (7 downto 0);

IN.6: in STD_LOGIC_VECTOR (15 downto 0);

OUTS: out STD_LOGIC_VECTOR (15 downto 0);

IN.2: in STD_LOGIC_VECTOR (31 downto 0);

OUTS2: out STD_LOGIC_VECTOR (31 downto 0);

library IEEE;

use IEEE.std_logic_1164.all;

```

# **VHDL**

Dataflow Design (2) -

```

endritecture prime2_arch of prime is signal N3L_N0, N3L_N2L_N1, N2L_N1_N0, N2_N1L_N0: STD_LOGIC; begin c= not N(3) and not N(2) and N(1); N3L_N2L_N1 c= not N(3) and not N(2) and N(1) and N(0); N2L_N1L_N0 c= not N(2) and not N(1) and N(0); N2L_N1L_N0 c= N2_N1L_N0 c= N2L_N1L_N0 or N3L_N3L_N1 or N3L_N1_N0 or N3L_N1L_N0; end prime2_arch;

```

### 5. VHDL

Behavioural Design (1) -

- The main behavioural construct is the <u>process</u> which is a collection of sequential statements that executes in parallel with other concurrent statements and processes.

- A process simulates in zero time.

- A VHDL process is a concurrent statement, with the syntax:

```

sequential-statement

process (signal-name, speedectarations variable declarations constant declarations function definitions procedure definitions seguential-statement sequential-statement

```

### **VHDL**

- A process can not declare signals, only variables, which are used to keep track of the process state.

The syntax for defining a variable is: variable variable-names : variable-type;

A VHDL process is either running or suspended

- the process runs. The list of signals in the process definition (sensitivity list) determines when

- A process is initially suspended. When a sensitivity list's signal changes value, the process resumes, starting at the 1st statement until the end.

- If any signal in the sensitivity list change value as a result of running the process, it runs again.

## **VHDL**

Behavioural Design (3) -

- value. This continues until the process runs without any of these signals changing

- In simulation, this happens in zero simulation time.

- Upon resumption, a properly written process will suspend after a couple of

- It is possible to write an incorrect process that never suspends.

- Consider a process with just one sequential statement "x <= not x;" and a sensitivity list of "(x)".

- Since X changes on every pass, the process will run forever in zero simulated

- In practice, simulators can detect such behaviour, to end the simulation.

### YHDL

Behavioural Design (4) -

- concurrent version (but it occurs within the body of a process): The sequential signal assignment statement has the same syntax as the signal-name <= expression;

- The variable assignment statement has the following syntax:

```

expression;

```

```

N3L_N0 := not N(3)

N3L_N2L_N1 := not N(3) and not N(2) and N(1) and N(0);

N2L_N1L_N0 := not N(2) and not N(1) and N(0);

N2_N1L_N0 := not N(2) and not N(1) and N(0);

N2_N1L_N0 := not N3L_N2L_N1 or N2L_N1_N0 or N2_N1L_N0;

end process;

nd prime6_arch;

process(N)

variable N3L_N0, N3L_N2L_N1, N2L_N1_N0, N2_N1L_N0: STD_LOGIC:

itecture prime6_arch of prime6 is

```

### YHDL

Behavioural Design (5) -

Other sequential statements include popular constructs, such as if, case, loop, for, and while.

```

if boolean-expression then sequential-statement else sequential-statement end if;

if boolean-expression then end if;

```

if boolean-expression then sequential-statement elsif boolean-expression then sequential-statement elsifboolean-expression then sequential-statement end if; if boolean-expression then sequential statement elsif boolean-expression then sequential statement

> Loop sequential-statement sequential-statement end loop; when choices => sequential-statements end case; for identifier in range loop sequential-statement sequential-statement end loop;

case expression is when choices => sequential-statements

while boolean-expression loop sequential-statement sequential-statement end Loop;

els.fboolean-expression then sequential-statement

else sequential-statement

end if;

### 5. VHDL

Behavioural Design (6) -

```

process(N)

variable NI: INTEGER;

begin

NI: = CONTINTEGER(N);

NI: = CONTINTEGER(N);

if NI=1 or NI=2 then P <= '1';

elsif NI=3 or NI=5 or NI=7 or NI=11 or

NI=13 then P <= '1';

else P <= '0';

end process;

end process;

end prime7_arch;

```

process (N)

begin

case CONV\_INTEGER(N) is

when 1 => F <= '1',

when 2 => F <= '1',

when 3 | 5 | 7 | 11 | 13 => F

when there => F <= '0',

end case;

end process;

end primeS\_arch;

end primeS\_arch;

### 5. VHDL

Behavioural Design (7) -

```

NI := CONV_INTEGER(N);

prime == true;

if NI=1 or NI=2 then null; -- bound

else for i in 2 to 251 loop

else for i in 2 to 251 loop

if NI mod i = 0 then

prime := false; exit;

end if;

end iop;

if prime then p <= 'l'; else p <= 'l'

end process;

end prime 2_arch;

architecture prime9_arch

process(N)

variable NI: INTEGER;

variable prime: boolean;

begin

```

Time Dimension (1) -

- None of the previous examples deals with the time dimension of the circuit operation: everything happens in zero simulated time.

- VHDL has excellent facilities for modelling the time.

- VHDL allows a time delay to be specified by using the keyword after in any signal-assignment statement.

- '1' after 4ns when X='1' else '0' after 3ns;

- This models a gate that has 4ns of delay on a 0-to-1 output transition and only 3ns on a 1-to-0 transition.

- With these values, a VHDL simulator can predict the approximate timing behaviour of a circuit.

### **YHDL**

Simulation (1) -

- a simulator can be used to observe its operation. Once we have a VHDL program whose syntax and semantics are correct,

- Simulator operation begin at simulation time of zero

- At this time, the simulator initialises all signals to a default value.

- It also initialises any signals and variables for which initial values have been explicitly declared.

- statements) in the design. Next, the simulator begins the execution of all processes (and concurrent

- The simulator uses a time-based event list and a signal-sensitivity matrix to simulate the execution of all the processes.

### 5. VHDL

- Simulation (3) -

- If the assignment has an explicit simulation time (after clause), then it is scheduled on the event list to occur at that time.

- Otherwise, it is supposed to occur "immediately".

- delta delay It is actually scheduled to occur at the current simulation time plus one

- simulation time. The <u>delta delay</u> is an infinitesimally short time, such that the current simulation time plus any number of delta delays still equals the current

- The delta delay concept allows processes to execute multiple times (if necessary) in zero simulated time.

- After a simulation cycle completes, the event list is scanned for the signals that change at the next earliest time on the list.

### **YHDL**

Time Dimension (2) -

- Another way to invoke the time dimension is with wait. This sequential statement can be used to suspend a process for a specified time period.

- A wait statement can be used to create simulated input waveforms to test the operation of a circuit.

rehitecture InhibitTB\_arch of InhibitTestBench is omponent Inhibit port  $(X_rY: \text{in BIT}; Z: \text{out BIT})_r \text{ end conjugal } X_T, Y_T, ZT: \text{BIT}_r \text{ egin}$ inhibit port map (XT, YT, ZT);

ess 00; YT <= '0'; for 10 ns; '0'; YT <= '1'; for 10 ns; '1'; YT <= '0'; for 10 ns; '1'; YT <= '1'; --- this suspends

### 5. VHDL

Simulation (2) -

- At simulation time zero, all processes are scheduled for execution.

- One of them is selected and all of its sequential statements are executed, including any looping behaviour that is specified.

- and so on, until all processes have been executed. When the execution of this process is completed, another one is selected

- This completes one simulation cycle.

- During its execution, a process may assign new values to signals

- The new values are not assigned immediately. They are placed on the event list and scheduled to become effective at a certain time.

### 5. VHDL

Simulation (4)

- case the simulation time is advanced. This may be as little as one delta delay, or it may be a real delay, in which

- In any case, the scheduled signal changes are made.

- Some processes may be sensitive to the changing signals

- All the processes that are sensitive to a signal that just changed are scheduled for execution in the next simulation cycle.

- The simulator's operation goes on indefinitely until the list is empty.

- concurrent processes in a uni-processor system. The event list mechanism makes it possible to simulate the operation of

- of processes may require multiple executions. The delta delay mechanism ensures correct operation even though a set

#### <u>.</u> **YHDL**

Simulation (5) -

entity testAlulbit is

end entity test\_alulbit; architecture tst of testAlu1bit is component alubit is

port (

a, b, c : in std\_logic;

sel : in std\_logic\_vector (1

downto 0);

res, f : out \*\*\*

signal ii : std\_logic := '0'; signal ii : std\_logic := '0'; signal ci : std\_logic := '0'; signal op : std\_logic\_vector (I domnto 0) := "00"; signal res : std\_logic; signal co : std\_logic; res, f : out std\_logic);

end component alulbit;

```

begin

-- instanciar o sistema

-- a testar

-- a tulbit

process (il) is

begin

if il='1' then

il <='0' after lons;

elsif il='0' then

il <='1' after lons;

end if;

if i2='1' then

i2 <= '0' after 20ns;

elsif i2='0' then

i2 <= '1' after 20ns;

end if;

end process;</pre>

process (i2) i

begin

and process;

=> i1

=> i2

=> ci

=> co

=> co

>;

```

```

end process;

end architecture;

process (ci) is

begin

ci = '1' then

ci <= '0' after 40ms;

elsif ci='0' then

ci <= '1' after 40ms;

end if;

end process;

if op="00" then

op <= "01" after 80ns;

elstif op="01" then

op <= "10" after 80ns;

elstif op="10" then

op <= "11" after 80ns;

elstif op="11" then

op <= "00" after 80ns;

end if;

end process;

ocess (op) is

```

### 5. VHDL

Synthesis (1)

- VHDL was originally conceived as a description and simulation language

- It was later adopted also for synthesis purposes.

- synthesized The language has many features and constructs that can NOT be

- The code that is written can have a major impact on the quality of the far are generally synthesizable by most commercial tools. The subset of the language and the style of the programs presented so

- a corresponding serial chains of logic gates to test conditions Serial control structures, like if-elsif-elsif-else can result in synthesized circuits.

- It is better to use a case or select statement if the conditions are

- mutually exclusive.

### 5. VHDL

- Synthesis (2) -

- Loops in processes are usually unwound to create multiple copies of combinational logic to execute the statements in the loop.

- statements in the loop, then a sequential circuit must be designed. If one wants just one copy of the combinational logic to execute the

- When using conditional statements in a process, failing to include all the value that might otherwise change. input combinations will cause the compiler to introduce a latch to hold the old

- Such latches are typically not intended.

- Finally, some language features and constructs are simply unsynthesizable, depending on the tool being used.

- Typical examples include dynamic memory, files, and pointers