### Sistemas Digitais I

Combinational Principles

- Summary -

Circuit Analysis

LESI - 2º ano

Unit 4 - Combinational Systems Principles

#### João Miguel Fernandes www.di.uminho.pt/~jmf

Hazards

Karnaugh Maps Circuit Manipulations Circuit Synthesis

DEP. DE INFORMÁTICA ESCOLA DE ENGENHARIA UNIVERSIDADE DO MINHO

### 4. **Combinational Principles**

Circuit Analysis (1) -

- After having a formal description of the logic function, we can:

- Determine the behaviour of the circuit for various input combinations.

- Manipulate the algebraic description to suggest different circuit structures.

- Transform the algebraic description into a standard form (example: PLD). Use the algebraic description of the circuit to analyse a larger system that includes it as a subsystem.

### Combinational Principles

- Circuit Analysis (2) -

We can obtain the truth table by going through all input combinations

- From the truth table we can directly write a logic expression.

- This technique is time-consuming and only works for small number of input variables.

### **Combinational Principles**

Circuit Analysis (3) -

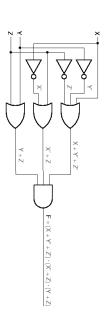

From inputs to outputs

$F = ((X+Y') \cdot Z) + (X' \cdot Y \cdot Z')$

### 4. Combinational Principles

Circuit Analysis (4) -

- After some algebraic transformation

- $F = ((X+Y') \cdot Z) + (X'\cdot Y \cdot Z')$  $= (X\cdot Z) + (Y'\cdot Z) + (X'\cdot Y \cdot Z')$

Circuit Analysis (5) -

```

П

= ((X+Y') \cdot Z) \cdot (X'Y'Z')

= (X+Y'+X') \cdot (X+Y'+Y) \cdot (X+Y'+Z') \cdot (Z+X') \cdot (Z+Y') \cdot (Z+Y') \cdot (Z+Z')

= 1 \cdot 1 \cdot (X+Y'+Z') \cdot (X+Z') \cdot (Z+Y') \cdot 1 =

= (X+Y'+Z') \cdot (X'+Z) \cdot (Y+Z)

```

### **Combinational Principles**

Circuit Synthesis (1) -

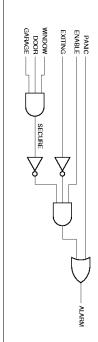

- written in natural language (Portuguese, for example). The starting point for designing combinational circuits is usually a description

- Example: Construction of an alarm circuit.

- "The ALARM output is 1 if the PANIC input is 1, or if the ENABLE input is 1, the EXITING input is 0, and the house is not secure. The house is secure if the WINDOW, DOOR and GARAGE inputs are all 1".

- ALARM = PANIC + ENABLE EXITING' SECURE' SECURE = WINDOW DOOR GARAGE

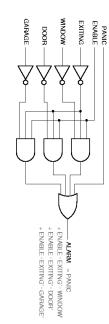

#### 4. Combinational Principles

Circuit Synthesis (2)

- ALARM SECURE = WINDOW:DOOR:GARAGE = PANIC + ENABLE EXITING' SECURE'

- ALARM = PANIC + ENABLE EXITING (WINDOW DOOR GARAGE)

- ALARM = PANIC + ENABLE EXITING' (WINDOW' + DOOR' + GARAGE')

- ALARM

### Combinational Principles

Circuit Synthesis (3) -

- which a signal should be on or off (equivalent to a truth table). Other times, the description starts with a list of the input combinations for

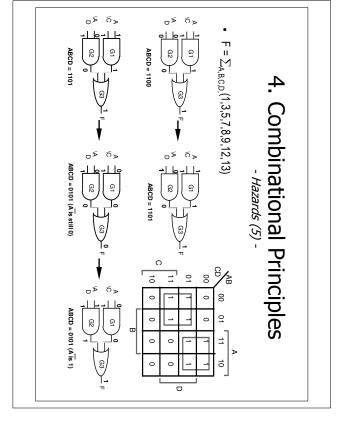

- output for N=1,2,3,5,7,11,13." Example: Construction of a circuit that detects 4-bit prime numbers "Given a 4-bit input combination N=N<sub>3</sub>N<sub>2</sub>N<sub>1</sub>N<sub>0</sub>, the circuit produces a 1

- $$\begin{split} F &= \sum_{N_3,N_2,N_1,N_0} (1,2,3,5,7,11,13) = \\ N_3\cdot N_2\cdot N_1\cdot N_0 + N_3\cdot N_2\cdot N_1\cdot N_0 \cdot + N_3\cdot N_2\cdot N_1\cdot N_0 \end{split}$$

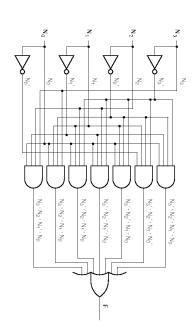

#### 4 **Combinational Principles**

Circuit Synthesis (4) -

### **Combinational Principles**

Circuit Manipulations (1) -

- We have described methods that use AND, OR, and NOT gates

- faster than ANDs and ORs in most technologies). In some situations, we might like to use NAND or NOR gates (they are

- However, most people don't develop logic propositions in terms of NAND and NOR connectives.

- Nobody says: "I don't like a girl, if she is not smart or not pretty and also if she is not rich or not friendly".  $[G' = (S'+P') \cdot (R'+F')]$

- It is more common to say: "I like a girl, if she is smart and pretty or if she is rich and friendly". [G = (S·P) + (R·F)]

- Any logic expression can be transformed into an equivalent sum-of-products (SOP) expression and implement with AND and OR gates

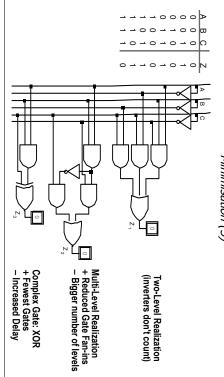

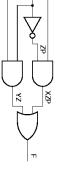

- Circuit Manipulations (2) -

A 2-level AND-OR circuit may be converted to a 2-level NAND-NAND circuit simply by substituting gates.

If any product terms in the sum-of-products expression contain just a single literal, inverters may appear or disappear.

### 4. Combinational Principles

- Circuit Manipulations (3) -

- Any sum-of-products (SOP) expression can be realised in either two ways (AND-OR circuit or NAND-NAND circuit).

- The principle of duality can be applied to this rule:

Any product-of-sums (POS) expression can be realised in either two ways (OR-AND circuit or NOR-NOR circuit).

### 4. Combinational Principles

- Circuit Manipulations (4) -

These manipulations can be applied to arbitrary logic circuits.

The (d) solution is better than the (c) solution.

### 4. Combinational Principles

Circuit Manipulations (5) -

- Any set of logic-gate types that can realize any logic function is called a complete set.

- 2-input AND gates, 2-input OR gates and inverters form a complete set

- Any logic function can be expressed as a sum-of-products of variables and their complements, and AND and OR gates with any number of inputs can be made from 2-input gates.

2-input NAND gates form a complete set.

## Combinational Principles

Minimisation (1) -

- It is uneconomical to realise a logic function directly from the first expression that comes up.

- Canonical (sum and product) expressions are especially expensive.

- Logic minimisation uses several techniques to obtain the simplest gatelevel implementation of a Boolean function.

- But simplicity depends on the metric used.

- Three possible metrics that can be used are:

- number of literals

- number of gates

- number of cascaded levels of gates

## 4. Combinational Principles

Minimisation (2)

- The <u>number of literals</u> measure the amount of wiring needed to implement a function

- The <u>number of gates</u> measures circuit area.

- There is a relation between the number of gates in a design and the number of components needed for its implementation.

- The <u>number of levels of gates</u> is related with the circuit's delay.

- Reducing the number of levels reduces overall delay.

- However, putting a circuit in a form suitable for minimum delay rarely yields an implementation with the fewest or simplest gates.

- It is not possible to minimise all three metrics at the same time.

Minimisation (3) -

### Combinational Principles

- Minimisation (4) -

- Minimisation techniques reduce the number and size of gates that are needed to build a circuit, thus decreasing the cost of the system.

- AND circuit by: The minimisation methods reduce the cost of a 2-level AND-OR or OR-

- minimising the number of first-level gates;

- minimising the number of inputs on each first-level gate;

minimising the number of inputs on each second-level gate;

#### 4. Combinational Principles

- Minimisation (5) -

- The minimisation methods do not consider the cost of input inverters

- They assume that both true and complement versions of all input variables are available (appropriate for PLD-based design).

- truth table or as a minterm or maxterm list. They also assume that the function to be minimised is represented as a

- Minimisation is based on theorems T10 and T10' product:Y + product:Y' = product

- $(sum+Y) \cdot (sum+Y') = sum$

- One gate is saved and the remaining one has one fewer input

term with one less variable.

If two terms differ only in one variable, they can be combined into a single

#### 4. Combinational Principles

- Minimisation (6) -

B's values change within the on-set rows A's values don't change within the on-set rows B is eliminated, A remains

B's values stay the same within the on-set rows A's values change within the on-set rows A is eliminated, B remains

Essence of Simplification:

Find two element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

### **Combinational Principles**

Minimisation (7) -

- Let us apply this technique to the prime-number detector function

Let us apply .... =  $F = \sum_{N_5,N_6,N_6,N_6,N_6} (1,2,3,5,7,11,13) = \\ N_3 \cdot N_2 \cdot N_1 \cdot N_0 + \dots = \\ (N_3 \cdot N_2 \cdot N_1 \cdot N_0 + N_3 \cdot N_2 \cdot N_1 \cdot N_0) + (N_3 \cdot N_2 \cdot N_1 \cdot N_0 + N_3 \cdot N_2 \cdot N_1 \cdot N_0) + \\ \dots = (N_3 \cdot N_2 \cdot N_1 \cdot N_0 + N_3 \cdot N_2 \cdot N_1 \cdot N_0) + \dots = N_3 \cdot N_0 + \dots$

## Combinational Principles

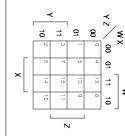

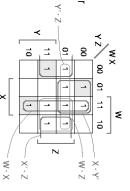

Karnaugh Maps (1) -

- It is hard to find terms that can be combined

- table. A Karnaugh map is a graphical representation of a logic function's truth

- minterm. The map for an n-input logic function is an array with 2n cells, one for each

Karnaugh Maps (2) -

- convenient as 2-, 3- and 4-variable maps, since adjacency is more difficult to The Karnaugh maps used to represent 5- and 6-variable functions are not as

- In a 5-variable map, we need to use 2 4-variable maps that are located next to each other.

- In this representation, we assume that one map is overlaid on top of

3-dimensional object the other, so as to create a

Each square is adjacent to 5 squares (4 on its map and 1

on the other one)

### **Combinational Principles**

Karnaugh Maps (3)

Kamaugh map. A 6-variable

8

U,V = 1,0

U,V = 1,1

#### 4. Combinational Principles

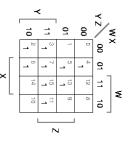

Karnaugh Maps (4) -

- To represent a logic function on a Karnaugh map, copy 1s and 0s from the truth table to the corresponding map's cells.

- Each map cell corresponds to a minterm of the function.

| _ | _ | _ | _ | 0 | 0 | 0 | 0 | × |

|---|---|---|---|---|---|---|---|---|

| _ | _ | 0 | 0 | _ | _ | 0 | 0 | ~ |

| _ | 0 | _ | 0 | _ | 0 | _ | 0 | Z |

| _ | 0 | _ | 0 | 0 | _ | _ | 0 | П |

|   |   |   |   |   |   |   |   |   |

In real life, we just copy 1s or 0s (not both) to the cells, depending on the expression we want to obtain (SOP or POS).

#### 4. Combinational Principles

- Karnaugh Maps (5) -

- Why that strange ordering of rows/columns?

- Each cell corresponds to an input combination that differs in only one variable from each of its immediately adjacent neighbours.

- Cells 7 and 15 in the 4-variable map differ only in the value of W.

- In the 3- and 4-variable maps, cells on the left/right or top/bottom borders are also neighbours.

- in the value of Y. Cells 8 and 10 in the 4-variable map differ only

- (product·Y + product·Y' = product) theorem T10 combined into a single product term, using Since pairs of adjacent 1-cells correspond to minterms that differ in one variable, they can be

#### 4 **Combinational Principles**

Karnaugh Maps (6) -

Minterm 5 is included twice. No

problems, since X+X=X.  $= X \cdot Z + Y \cdot Z + X \cdot Y \cdot Z'$

П

- Cells 5 and 7  $F = ... + X \cdot Y' \cdot Z + X \cdot Y \cdot Z$   $= ... + X \cdot Z$

- Cells 1 and 5  $F = X' \cdot Y' \cdot Z + X \cdot Y' \cdot Z + ...$   $= Y' \cdot Z + ...$

### Combinational Principles

Karnaugh Maps (7) -

- The cell-combining procedure can be extended to combine more than two 1cells into a single term.

- $$\begin{split} F &= \sum_{X,Y,Z} (0,1,4,5,6) = X \cdot Y \cdot Z' + X \cdot Y \cdot Z + X \cdot Y \cdot Z' + X \cdot Y \cdot Z' \\ &= [Y \cdot (X',Z') + Y \cdot (X',Z) + Y \cdot (X \cdot Z) + Y \cdot (X \cdot Z)] + X \cdot Y \cdot Z' \\ &= Y' + X \cdot Y \cdot Z' \end{split}$$

Karnaugh Maps (8) -

- In general, 2<sup>i</sup> 1-cells may be combined to form a product term containing n-i literals (n = number of variables).

- Rule for combining 1-cells:

- A set of 2! 1-cells may be combined if there are i variables that take on all 2! combinations within that set, while the remaining n-i variables have the same value throughout that set.

- The respective product term has n-i literals, where a variable is complemented if it appears as 0 in all of the 1-cells, and uncomplemented if it appears as 1.

- Graphically, we can circle rectangular sets of 2<sup>n</sup> 1-cells.

### 4. Combinational Principles

- Karnaugh Maps (9)

- From the 1-cell circles, obtain the corresponding product term:

- If a circle covers only areas of the map where the variable is 0 (1), then the variable is complemented (uncomplemented) in the product term.

- If a circle covers areas of the map where the variable is 0 and 1, then the variable does not appear in the product term.

### 4. Combinational Principles

- Karnaugh Maps (10) -

- A <u>minimal sum</u> of a logic function F is a sum-of-products expression for F such that no sum-of-products expression for F has fewer product terms, and any sum of products expression with the same number of product terms has at least as many literals.

- The minimal sum has the fewest possible product terms (1st level gates and 2<sup>nd</sup> level gate inputs) and the fewest possible literals (1st level gate inputs).

- A logic function P <u>implies</u> a logic function F (P ⇒ F) if for every input combination such that P=1, then F=1 also. F <u>includes</u> or <u>covers</u> P.

- A <u>prime implicant</u> of a logic function F is a normal product term P that implies

F, such that if any variable is removed from P, then the resulting product

term does not imply F.

### 4. Combinational Principles

Karnaugh Maps (11) -

- In terms of a Karnaugh map, a prime implicant of F is a circled set of 1-cells, such that if we try to make it larger (covering twice as many cells), it covers one or more 0s.

- Prime-Implicant Theorem: A minimal sum is a sum of prime implicants.

- To find a minimal sum, we need not consider any product terms that are not prime implicants.

- The sum of all the prime implicants of a function is called a complete sum

- The complete sum is not necessarily a minimal one.

### 4. Combinational Principles

- Karnaugh Maps (12) -

# Algorithm: Minimum SOP Expression from a Karnaugh Map

Step 1: Choose a "1" not already covered by an implicant.

Find "maximal" groupings of 1s (and Xs) adjacent to that element.

Remember to consider top/bottom row, left/right column, and corner adjacencies. This forms a prime implicant.

Repeat Step 1 to find all prime implicants.

Step 2: Visit a "1". If it is covered by a single prime implicant, it is essential, and participates in the final expression. The 1s covered by it do not need to be revisited.

Repeat Step 2 until all essential prime implicants have been found.

tep 3: If there remain 1s not covered by essential prime implicants, then select the smallest number of prime implicants that cover the remaining 1s.

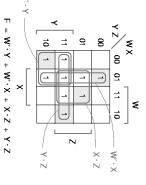

## 4. Combinational Principles

- Karnaugh Maps (13) -

- $F = \sum_{W,X,Y,Z} (1,3,4,5,9,11,12,13,14,15)$

- The function has 5 prime implicants.

- The minimal sum includes only 3 prime implicants:

$F = X \cdot Y' + X' \cdot Z + W \cdot X$

How to determine which prime implicar to include?

- Karnaugh Maps (14) -

- A <u>distinguished 1-cell</u> of a logic function is an input combination that is covered by only one prime implicant.

- An <u>essential prime implicant</u> of a logic function is a prime implicant that covers one or more distinguished 1-cells.

- Essential prime implicants <u>must</u> be included in every minimal sum.

- The 1st step in the prime implicant selection is identifying the distinguished 1cells and including the corresponding prime implicants.

- Then, one needs only to determine how to cover the 1-cells, if any, that are not covered by the essential prime implicants.

### 4. Combinational Principles

- Karnaugh Maps (15) -

$F = \sum_{\mathbf{W}, \mathbf{X}, \mathbf{Y}, \mathbf{Z}} (2,3,4,5,6,7,11,13,15)$

### . Combinational Principles

4.

Combinational Principles

- Karmaugh Maps (16) -

Karnaugh Maps (17)

- Using duality, we can minimise product-of-sums expressions by looking at 0s at the Karnaugh map.

- Each 0 on the map corresponds to a maxterm

W. - Z

- An easier way to find minimal products is to find the minimal sum for F

- The 1s of F' are just the 0s of F.

- Once we have the minimal sum for F', we complement the result by using the generalised DeMorgan's theorem (T14), to obtain a minimal product for F.

- Example: F' = X·Y' + X'·Z + W·X

$$F = (X'+Y) \cdot (X+Z') \cdot (W'+X')$$

$F = \Sigma_{W,X,Y,Z}(0,1,2,3,4,5,7,14,15)$

$W \cdot Y' + W \cdot X' + W \cdot X \cdot Y + W'$

3 8

ਤ ∖8

### 4. Combinational Principles

Karnaugh Maps (18) -

- Sometimes the output of a function does not matter for certain input combinations, called <u>don't cares</u>.

- Example: A prime-number detector whose 4-bit input N is always a BCD digit. Minterms 10-15 should never occur.

- $F = \sum_{N_5,N_2,N_1,N_0} (1,2,3,5,7) + d(10,11,12,13,14,15)$

### 4. Combinational Principles

- Karnaugh Maps (19) -

- The procedure for circling sets of 1s is modified if don't cares (d's or Xs) are included.

- Allow d's to be included when circling sets of 1s, to make the sets as large as possible. This reduces the number of variables in the corresponding prime implicants.

- Do not circle any sets that contain only d's. Including the corresponding product term in the function would unnecessarily increase its cost.

- The remainder of the procedure is the same.

- In particular, we look for distinguished 1-cells and not for distinguished d-cells.

- We also include only the corresponding essential prime implicants, and any others that are needed to cover all the 1s on the map.

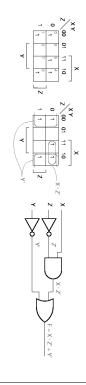

Karnaugh Maps (20) -

Example:  $F = \sum_{A,B,C,D} (4,5,6,8,9,10,13) + d(0,7,15)$

Initial Karnaugh map

Primes around m<sub>4</sub>=A' B C' D'

Primes around m<sub>5</sub>=A' B C' D

### Combinational Principles

Karnaugh Maps (21) -

Example continued

Primes around m<sub>13</sub>=A B C' D'

Primes around m<sub>8</sub>=A B' C' D'

Essential primes with minimum cover

#### 4. Combinational Principles

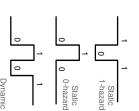

Hazards (1) -

- Due to delays on electronic devices, a circuit may produce a glitch.

- A glitch is a shorth-duration change in the output value, when no change is expected

- A hazard exists when a circuit has the possibility of producing a glitch.

- expected to remain unchanged. A static hazard occurs when it is possible for an output to undergo a momentary transition when it is

- A dynamic hazard occurs when the output has the expected to make a single transition. potential to change more than once when it is

### **Combinational Principles**

Hazards (2)

- variable, both give 1 as output, such that a momentary 0 output may occur during a transition in the differing input variable. A static-1 hazard is a pair of input combinations that differ only in one input

- X=Y=1. Z is changing from 1 to 0

Methods for eliminating hazards assume that only one input changes at a time. This assumption is equivalent to moving along neighbour cells in a Karnaugh map.

### **Combinational Principles**

Hazards (3)

- Karnaugh maps can be used to detect static

- A well designed 2-level sum-of-products circuit

- No single product term covers combinations may only have static-1 hazards

XYZ=111 and XYZ=110.

- changes before the gate that goes to 1). momentarily to 0 (if the gate that goes to 0 It is possible for the output to glitch

- must be included To eliminate the hazard, an extra AND gate

$F = X \cdot Y' \cdot Z' + W' \cdot Z + W \cdot Y$

$F = X \cdot Y' \cdot Z' + W' \cdot Z + W \cdot X \cdot Z'$

## Combinational Principles

Hazards (4)

To eliminate the hazard, an extra AND gate must be included 9 8 ž